VHDL là gì?

Thiết kế VHDL từ viết tắt của cụm từ Very High Speed Intergrated Circuit Hardware Description Language là quá trình sử dụng ngôn ngữ mô tả phần cứng (HDL) để mô tả và thiết kế các hệ thống điển tử kỹ thuật số được sử dụng rộng rãi trong ngành công nghiệp điện tử.

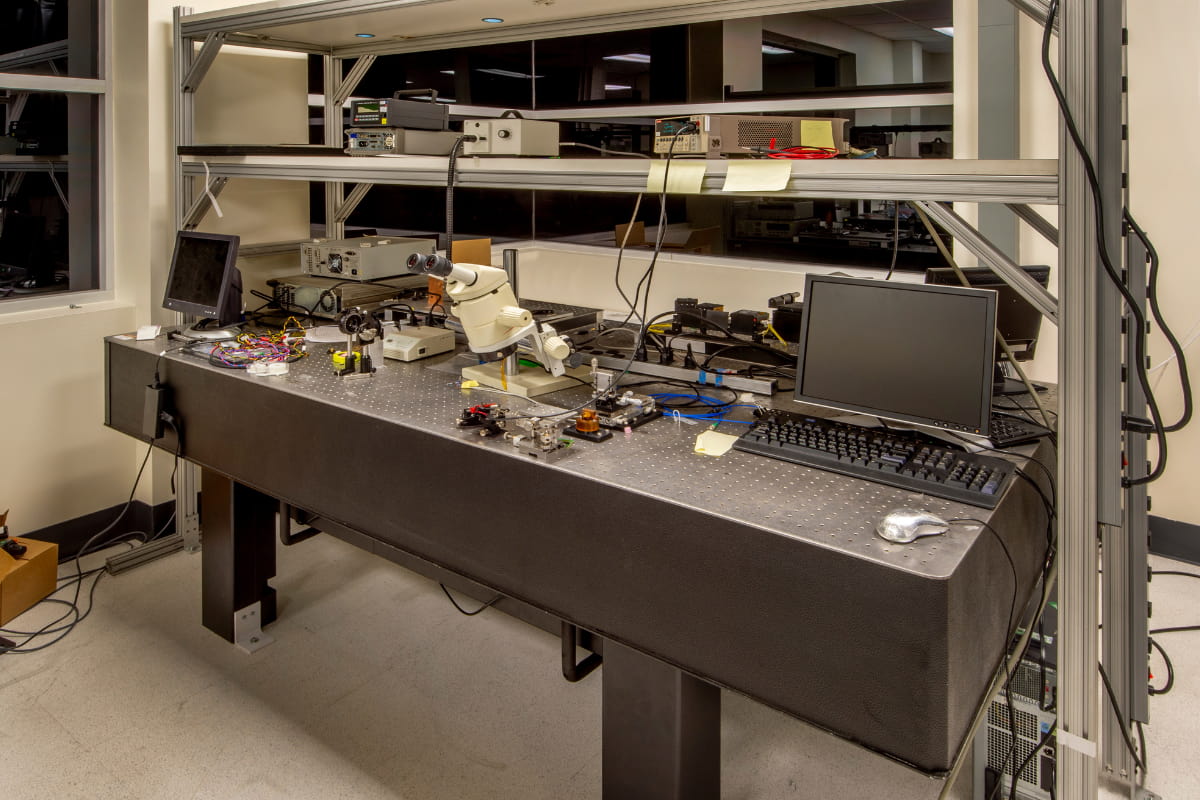

Thiết kế vhdl (nguồn: internet)

Ưu điểm VHDL

-

Tính công cộng: VHDL được phát triển dưới sự bảo trợ của chính phủ Mỹ và hiện nay đã có tiêu chuẩn của IEEE, VHDL không thuộc sở hữu của bất kỳ cá nhân hay tổ chức nào. Do đó VHDL được hỗ trợ nhiều nhà sản xuất thiết bị cũng như cung cấp các thiết kế. Đây là ưu điểm nổi bật của VHDL và giúp nó ngày càng phổ biến.

-

Khả năng hỗ trợ nhiều công nghệ và phương pháp thiết kế: VHDL cho phép thiết kế bằng nhiều phương pháp thiết kế từ trên xuống dưới hay ngược lại dựa vào thư viện sẵn có. Nó phục vụ tốt cho nhiều mục đích thiết kế từ các phần tử phổ biến đến các thiết kế đặc biệt như Application Specified IC.

-

Độc lập với công nghệ: Độc lập với công nghệ chế tạo phần cứng. Mô tả hệ thống thiết kế thành các bảng tổng hợp mạch khác nhau tùy vào mục đích sử dụng.

-

Khả năng mô tả mở rộng: Khả năng mô tả hoạt động dựa trên nhiều mức nhưng chỉ sử dụng một cú pháp chặt chẽ để thống nhất.

-

Khả năng trao đổi kết quả: T Được chấp nhận là một tiêu chuẩn, nên mô hình VHDL có thể chạy mọi bộ mô phỏng đáp ứng tiêu chuẩn và các kết quả môt tả trên hệ thống có thể trao đổi được với nhà thiết kế.

-

Khả năng hỗ trợ thiết kế mức lớn và khả năng sử dụng lại các thiết kế: Là một ngôn ngữ lập trình bậc cao, vì thế VHDL được sử dụng để thết kế một hệ thống lớn với sự tham gia của nhiều người cùng một nhóm.

Các dạng thiết kế VHDL

Thiết kế VHDL có 2 dạng thiết kế thường thấy là RTL sử dụng HDL và Test bench (TB): Thiết kế RTL sử dụng HDL: VHDL

Để mọi người có thể hiểu rõ các thuật ngữ trên thì sau đây là khái niệm về rtl, hdl, vhdl, verilog:

-

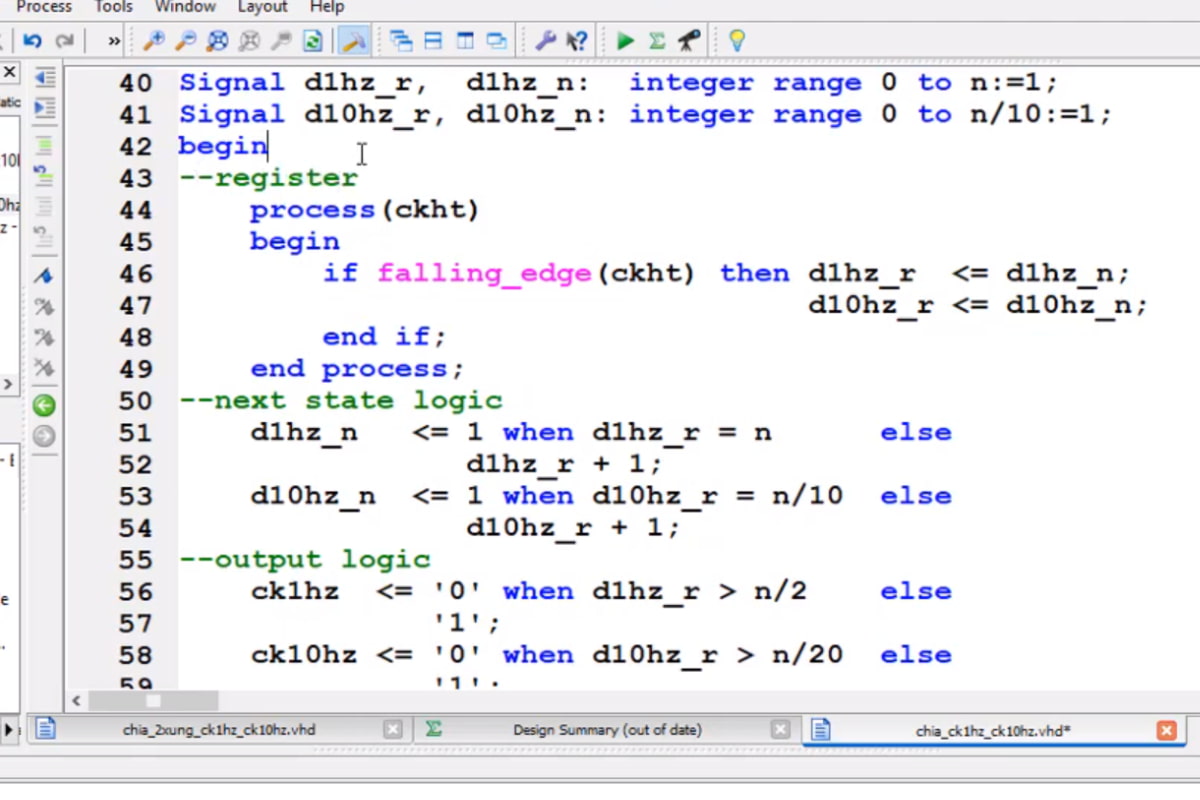

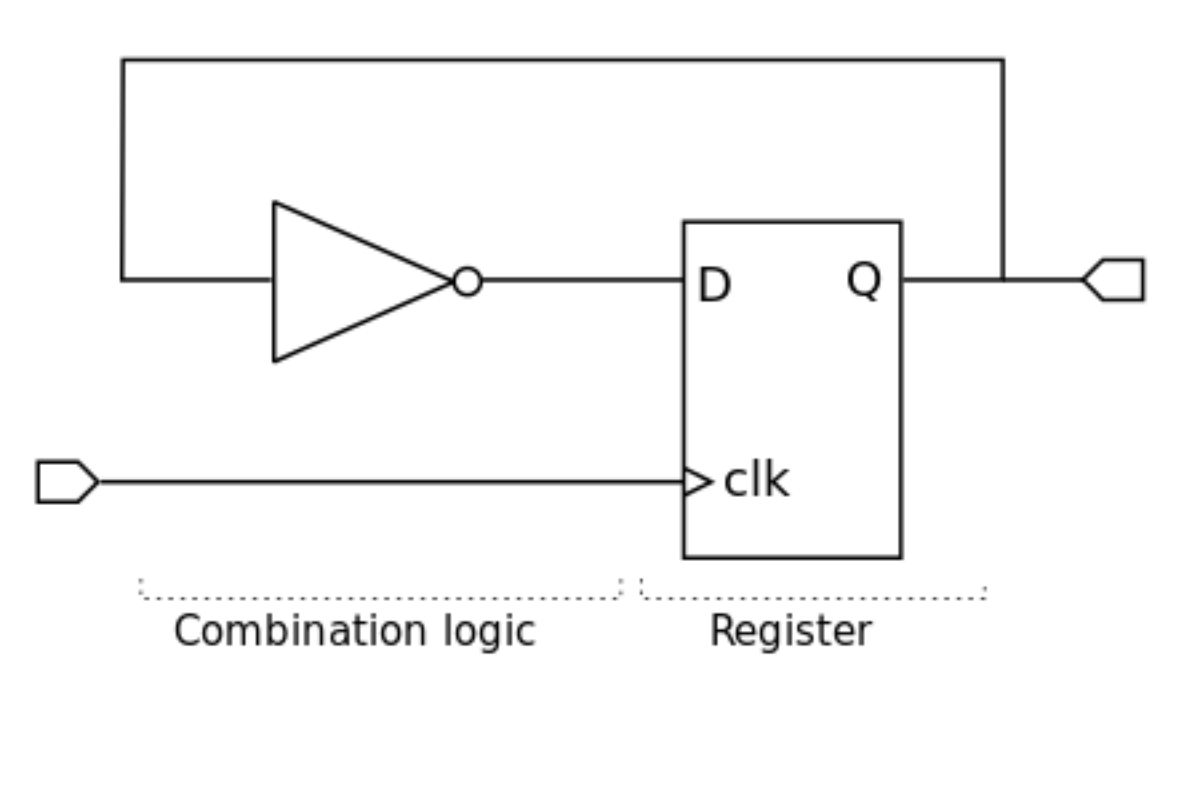

RTL là viết tắt của “Register Transfer Level”, là một cấp độ trừu tượng trong thiết kế phần cứng kỹ thuật số. RTL mô tả hệ thống dưới dạng tập hợp các bộ lưu trữ (register) và các tín hiệu truyền từ bộ nhớ này sang bộ nhớ khác.

RTL (nguồn: wikipedia)

-

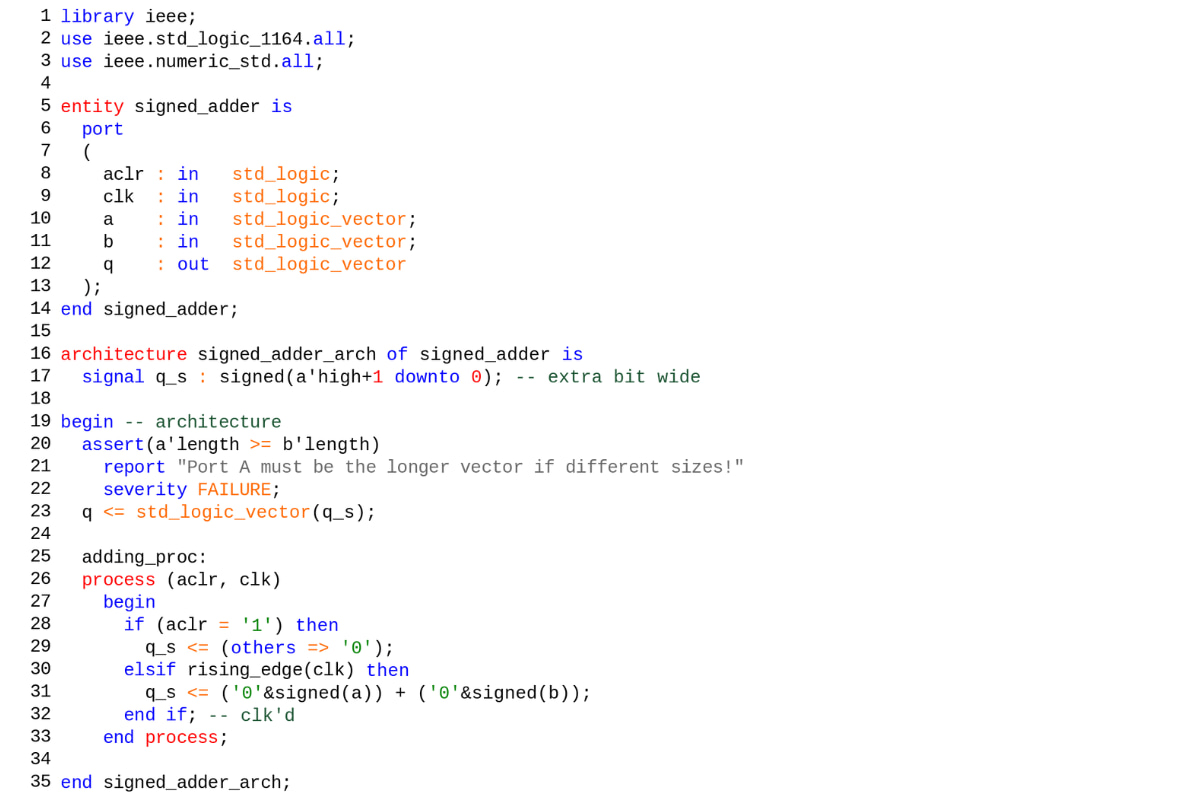

HDL là viết tắt của “Hardware Description Language” (Ngôn ngữ mô tả phần cứng). HDL là một loại ngôn ngữ lập trình được sử dụng để mô tả và thiết kế các hệ thống điện tử kỹ thuật số.

HDL (nguồn: wikipedia)

-

VHDL một trong những ngôn ngữ mô tả phần cứng (HDL) phổ biến nhất được sử dụng trong việc thiết kế và mô tả các hệ thống điện tử kỹ thuật.

Dưới đây là các bước cơ bản để sử dụng thiết kế vhdl khi thiết kế rtl:

-

Xác định yêu cầu và thiết kế: Trước khi bắt đầu viết mã VHDL, bạn cần phải có một hiểu biết rõ ràng về yêu cầu của mạch bạn đang thiết kế. Xác định các chức năng, cổng I/O, và các tính năng khác mà mạch cần thực hiện.

-

Viết mã VHDL: Sử dụng một trình soạn thảo VHDL để viết mã. Trong VHDL, bạn sẽ mô tả cách các thành phần của mạch liên kết với nhau, bao gồm các bộ đăng ký, các cổng, bộ chuyển đổi, và các phần khác của mạch. Đảm bảo mã của bạn tuân theo cú pháp và cấu trúc của VHDL.

-

Kiểm tra và mô phỏng: Sau khi viết mã, sử dụng công cụ mô phỏng VHDL để kiểm tra tính đúng đắn của mạch của bạn. Mô phỏng giúp bạn kiểm tra các kịch bản hoạt động khác nhau và đảm bảo mạch hoạt động như mong đợi.

-

Tổng hợp và triển khai: Sau khi mã của bạn đã được kiểm tra và mô phỏng, bạn có thể sử dụng công cụ tổng hợp để chuyển mã VHDL thành một mạch logic cụ thể, chẳng hạn như một mạch FPGA hoặc một mạch ASIC.

-

Kiểm tra trên phần cứng thực tế (nếu cần): Nếu có thể, sau khi triển khai, kiểm tra mạch của bạn trên phần cứng thực tế để đảm bảo rằng nó hoạt động đúng đắn trong môi trường thực tế.

-

Hiệu chỉnh và tối ưu hóa: Dựa trên kết quả của kiểm tra trên phần cứng thực tế, bạn có thể cần phải hiệu chỉnh và tối ưu hóa mã VHDL của mình để cải thiện hiệu suất hoặc khắc phục các vấn đề.

Test bench (TB) sử dụng: VHDL

Test bench là một môi trường mô phỏng hoặc kiểm tra độc lập được tạo ra để kiểm tra hoặc mô phỏng một mạch điện tử (circuit), một module hoặc một hệ thống phức tạp hơn.

Test bench

Để thiết kế một test bench bằng VHDL, bạn cần tạo một môi trường mô phỏng độc lập để kiểm tra mạch VHDL của bạn. Dưới đây là một số bước cơ bản để thiết kế một test bench VHDL:

-

Xác định yêu cầu kiểm tra: Trước hết, xác định các chức năng và tính năng cần được kiểm tra trong mạch VHDL của bạn. Xác định các tín hiệu đầu vào và các điều kiện biên mà bạn muốn thử nghiệm.

-

Viết mã VHDL cho test bench: Tạo một module test bench riêng biệt từ mạch VHDL chính của bạn. Test bench này sẽ tạo ra các tín hiệu đầu vào, cung cấp chúng cho mạch VHDL, và sau đó kiểm tra các tín hiệu đầu ra của mạch để đảm bảo rằng chúng phản ánh chính xác các chức năng được yêu cầu.

-

Tạo các tín hiệu đầu vào: Trong test bench, tạo các tín hiệu đầu vào mà mạch VHDL của bạn mong đợi. Điều này bao gồm tạo ra các tín hiệu đầu vào và gán giá trị cho chúng theo các điều kiện kiểm tra khác nhau.

-

Kích hoạt mạch VHDL: Sử dụng tín hiệu đầu vào đã tạo, kích hoạt mạch VHDL của bạn bằng cách gắn nó với test bench.

-

Kiểm tra các tín hiệu đầu ra: Theo dõi các tín hiệu đầu ra của mạch VHDL trong test bench và so sánh chúng với các kết quả mong đợi. Đảm bảo rằng mạch hoạt động chính xác dưới tất cả các điều kiện kiểm tra.

-

Tạo tập tin kiểm tra (test vector file) nếu cần: Đôi khi, bạn có thể muốn tạo các tập tin kiểm tra chứa các giá trị đầu vào và kết quả mong đợi. Điều này giúp quản lý và tái sử dụng các kịch bản kiểm tra.

-

Mô phỏng và debug: Sử dụng trình mô phỏng VHDL để chạy test bench và kiểm tra kết quả. Nếu có lỗi, sử dụng các công cụ debug để định vị và sửa chữa chúng.

-

Kiểm tra trên phần cứng thực tế (nếu cần): Sau khi test bench chạy thành công trên mô phỏng, bạn có thể muốn kiểm tra mạch của mình trên phần cứng thực tế để đảm bảo rằng nó hoạt động như mong đợi.

Việc thiết kế test bench là một phần quan trọng của quy trình thiết kế phần cứng và giúp đảm bảo rằng mạch của bạn hoạt động chính xác và đáng tin cậy trong mọi tình huống.

Các công việc và mức lương liên quan thiết kế VHDL

Các công việc liên quan:

Với các ưu thế của thiết kế VHDL mang lại nhiều ngành nghề, cùng với cơ hội phát triển đầy chuyển vọng vì thế ngành nghề này đòi hỏi sự chuyên sâu trong công việc. Thay vì nắm bắt nhiều kiến thức thì VHDL cần sự chuyên sâu trong một lĩnh vực nhất định. Một số công việc thiết kế VHDL cụ thế như:

-

Kỹ sư thiết kế FPGA/ASIC: Làm việc phát triển và tối ưu hóa các thiết kế FPGA hoặc ASIC, bao gồm việc viết mã VHDL để mô tả và kiểm tra các thiết kế phàn cứng.

-

Kỹ sư phát triển hệ thống nhúng: Phát triển các thiết bị điện tử tiêu dùng, ô tô, các thiết bị công nghiệp bằng cách triển khai các phần cứng trong hệ thống nhúng.

-

Nhà phân tích và kiểm tra phần cứng: Đảm bảo và đáo ứng các yêu cầu về hiệu suất và độ tin cậy trong khi thực hiện các bài kiểm tra và phân tích.

-

Kỹ sư bảo trì và hỗ trợ kỹ thuật: Hỗ trợ kỹ thuật cho các thiết keese phần cứng và thực hiện cập nhật hoặc sửa chữa các thiết bị cần thiết.

-

Kỹ sư tích hợp hệ thống: Tích hợp các thành phần cứng và phần mềm vào một hệ thống hoàn chỉnh.

-

Chuyên gia đào tạo và tư vấn: Chuyên gia đào tạo và tư vấn cho các tổ chức hoặc doanh nghiệp thiết kế VHDL và các công nghệ liên quan.

Mức lương:

Mức lương của một chuyên gia thiết kế VHDL thường biến động theo kinh nghiệm, quy mô tổ chức và vị trí địa lý. Trung bình mức lương thiết kế VHDL khoảng 60.000 USD ~ 90.000 USD mỗi năm.

Với chương trình đào tạo về thiết kế vhdl tại FPT Jetking, bạn sẽ được hướng dẫn và đào tạo một cách chuyên sâu về ngôn ngữ mô tả phần cứng VHDL. Chương trình này cung cấp kiến thức và kỹ năng cần thiết để thiết kế và mô phỏng các mạch điện tử, từ thiết kế cho rtl đến test bench. Bạn sẽ có cơ hội thực hành và áp dụng kiến thức vào thực tế, chuẩn bị cho sự nghiệp trong lĩnh vực thiết kế phần cứng. Đến với FPT Jetking, bạn sẽ trang bị cho mình những kỹ năng cần thiết để thành công trong ngành công nghiệp điện tử và viễn thông.

Với kinh nghiệm và môi trường đào tạo chuyên nghiệp. FPT Jetking tự tin trong việc đào tạo sinh viên về VHDL. Chúng tôi đang tổ chức khóa học chuyên sâu về thiết kế vi mạch bán dẫn. Vhdl là phần nội dung trong kỳ 3 của chương trình đào tạo. Với thời gian kéo dài trong 2 năm, khóa học này phù hợp cho sinh viên, học sinh và người đi làm. Đừng ngần ngại liên hệ với chúng tôi ngay nếu bạn quan tâm đến khóa học này!