Sinh viên FPT Jetking thực hiện đồ án thiết kế và tích hợp PLL vào SoC trên nền tảng Caravel, tiếp cận quy trình tapeout thực tế và kỹ thuật IC design chuyên sâu.

Giới thiệu đồ án thiết kế vi mạch mang tính thực tiễn cao

Trong lĩnh vực thiết kế vi mạch hiện đại, việc tiếp cận các bài toán gần với quy trình công nghiệp là yếu tố quan trọng giúp sinh viên phát triển năng lực chuyên môn. Một trong những đồ án tiêu biểu tại FPT Jetking là dự án “Design and SoC Integration of a PLL Macro in Caravel Platform”, được thực hiện bởi nhóm sinh viên lớp C1.2411.E0 gồm Nguyễn Vũ Mạnh Bảo, Nguyễn Trường Trung và Trần Nguyễn Diểm Quỳnh.

Đây là đồ án học kỳ 3 thuộc chuyên ngành thiết kế vi mạch, được đánh giá cao nhờ tính ứng dụng thực tế và mức độ tiếp cận gần với quy trình tapeout trong ngành công nghiệp bán dẫn.

Lý do lựa chọn đề tài: tiếp cận bài toán cốt lõi của IC design

Nhóm sinh viên đã lựa chọn đề tài liên quan đến thiết kế khối PLL (phase-locked loop), một thành phần quan trọng trong các hệ thống vi mạch hiện đại. PLL đóng vai trò then chốt trong việc tạo xung clock, tổng hợp tần số và đồng bộ hệ thống SoC.

Việc tích hợp một macro analog như PLL vào hệ thống SoC digital là một bài toán phức tạp trong thực tế, đòi hỏi sự hiểu biết sâu về cả thiết kế mixed-signal (kết hợp analog và digital) cũng như quy trình tích hợp hệ thống. Bên cạnh đó, việc sử dụng nền tảng Caravel – một framework mã nguồn mở phục vụ tapeout theo chuẩn OpenMPW – giúp sinh viên có cơ hội trải nghiệm quy trình thiết kế chip gần với môi trường doanh nghiệp.

Mục tiêu dự án: hoàn thiện quy trình thiết kế và tích hợp SoC

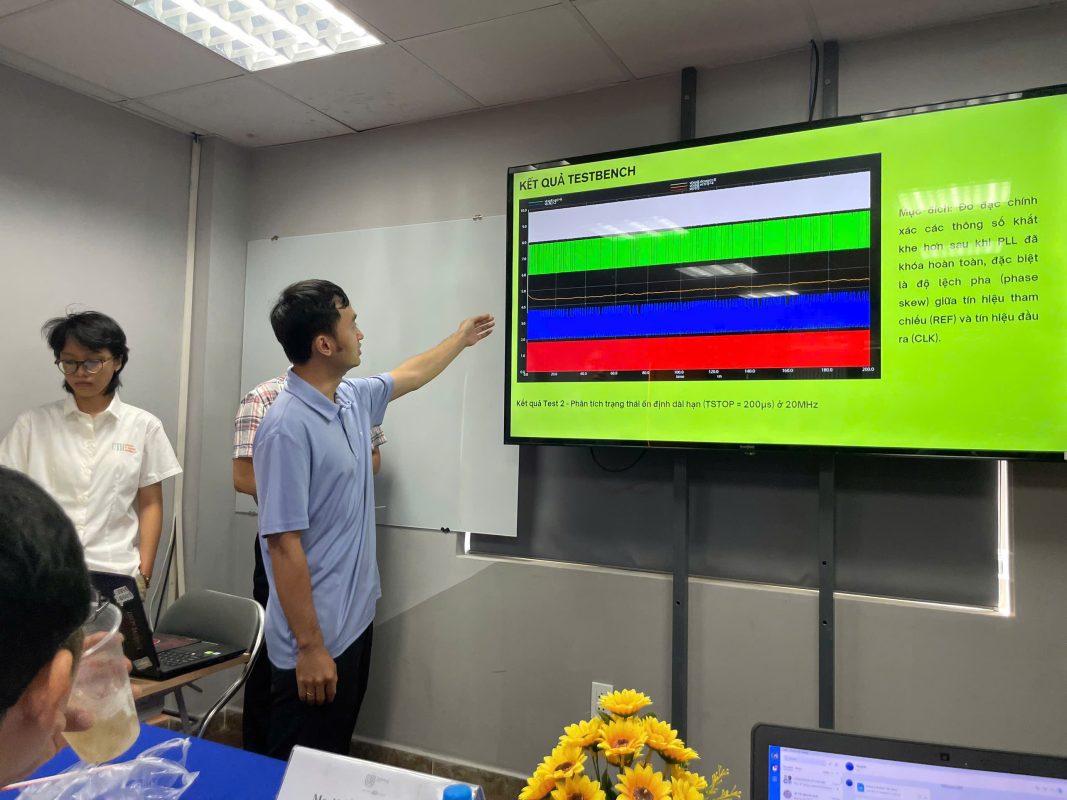

Dự án được triển khai với mục tiêu thiết kế một macro PLL ở mức layout dưới dạng black-box, đồng thời xây dựng đầy đủ các thành phần cần thiết như LEF, GDS và module Verilog. Không chỉ dừng lại ở thiết kế riêng lẻ, nhóm còn thực hiện tích hợp macro này vào hệ thống SoC thông qua Caravel user_project_wrapper.

Trong quá trình thực hiện, nhóm đảm bảo các yếu tố quan trọng như kết nối nguồn chính xác, mapping pin đúng chuẩn và không phát sinh lỗi DRC/LVS ở cấp độ toàn hệ thống. Đồng thời, toàn bộ flow thiết kế được triển khai thông qua OpenLane với đầy đủ các bước từ synthesis, floorplan, placement đến routing và signoff.

Quy trình triển khai: từ thiết kế macro đến tích hợp hệ thống

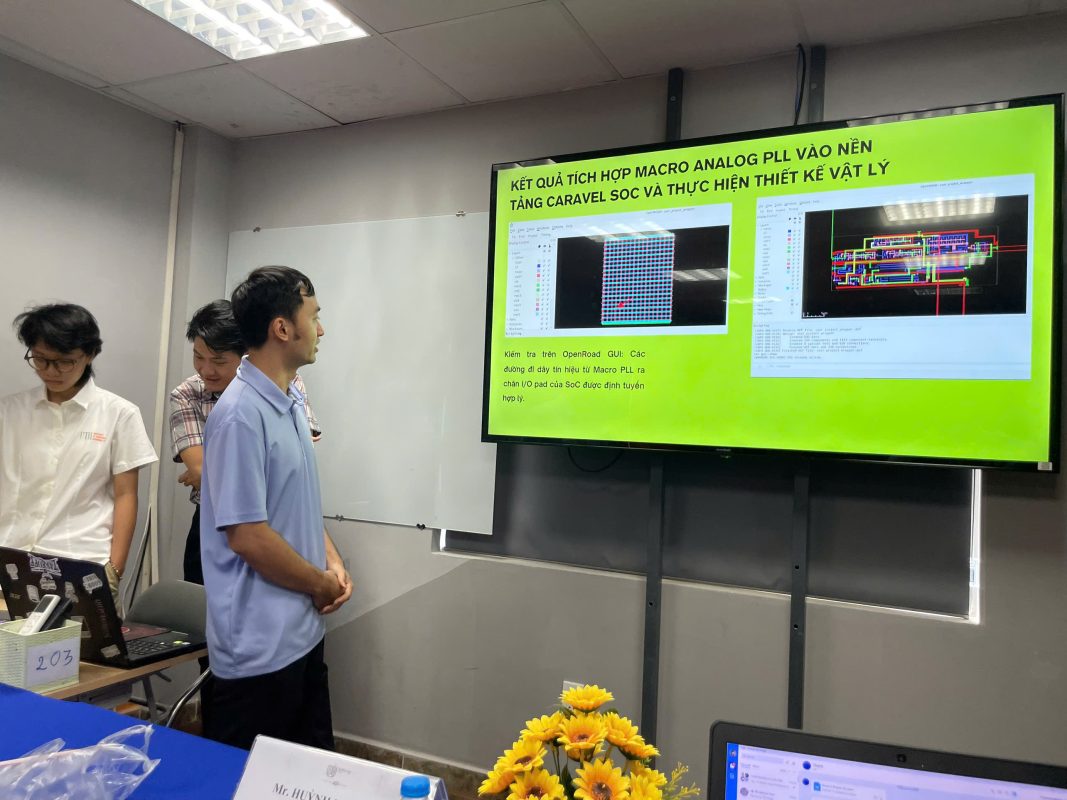

Quá trình thực hiện dự án được triển khai theo một flow chuẩn của ngành thiết kế vi mạch. Nhóm bắt đầu bằng việc thiết kế layout của PLL sử dụng công cụ Magic, sau đó định nghĩa các chân tín hiệu quan trọng như nguồn, clock và tín hiệu điều khiển. Từ layout này, các file GDS và LEF được export để phục vụ quá trình tích hợp.

Tiếp theo, nhóm xây dựng module Verilog dạng black-box, đảm bảo sự đồng bộ tuyệt đối giữa tên pin trong Verilog, LEF và layout. Việc tích hợp vào SoC được thực hiện thông qua Caravel bằng cách mapping tín hiệu vào hệ thống I/O và cấu hình macro placement.

Sau khi hoàn tất tích hợp, nhóm tiến hành chạy toàn bộ flow trên OpenLane và thực hiện các bước kiểm tra cuối cùng như DRC bằng Magic hoặc KLayout và LVS bằng Netgen để đảm bảo tính chính xác của hệ thống.

Thử thách thực tế và cách giải quyết

Trong quá trình thực hiện, nhóm đã đối mặt với nhiều thách thức điển hình của ngành IC design. Một trong những khó khăn lớn nhất là việc xử lý sự khác biệt giữa khối analog và hệ thống digital, đặc biệt khi PLL không có netlist transistor trong flow số, dẫn đến lỗi trong quá trình LVS.

Bên cạnh đó, việc không đồng bộ tên pin giữa các thành phần như LEF, Verilog và layout cũng gây ra các lỗi như unmatched pins, floating IO hoặc disconnected nets. Để giải quyết, nhóm đã áp dụng phương pháp định nghĩa PLL như một black-box đúng chuẩn, đồng thời đảm bảo sự đồng nhất tuyệt đối giữa các thành phần trong hệ thống.

Việc debug trong môi trường OpenLane với nhiều bước xử lý cũng là một thử thách, đòi hỏi kỹ năng đọc log và phân tích lỗi chi tiết – một kỹ năng quan trọng trong thiết kế vi mạch thực tế.

Tích hợp thành công macro analog vào SoC

Sau quá trình triển khai và tối ưu, nhóm đã tích hợp thành công macro PLL vào hệ thống SoC hoàn chỉnh. Dự án đáp ứng đầy đủ các tiêu chí kỹ thuật, từ việc chạy flow OpenLane đến kiểm tra DRC/LVS, đồng thời thể hiện rõ khả năng xử lý các vấn đề liên quan đến black-box macro và mismatch trong hệ thống.

Đây là một kết quả đáng ghi nhận, bởi việc tích hợp một khối analog vào hệ thống digital là một trong những bài toán khó trong ngành thiết kế chip.

Nền tảng cho kỹ sư vi mạch tương lai

Thông qua dự án, sinh viên đã hiểu sâu hơn về toàn bộ quy trình thiết kế SoC trong thực tế, từ thiết kế layout đến tích hợp hệ thống và kiểm tra vật lý. Đặc biệt, kỹ năng debug LVS và xử lý lỗi hệ thống được nâng cao rõ rệt, giúp sinh viên sẵn sàng tham gia vào các dự án IC design trong môi trường doanh nghiệp.

Việc làm việc với các công cụ như OpenLane, Caravel, Magic và KLayout cũng giúp người học làm quen với hệ sinh thái công cụ thực tế của ngành bán dẫn.

Theo nhận xét từ giảng viên, đây là một đồ án có độ khó cao và mang tính thực tiễn rõ rệt. Nhóm đã triển khai đúng quy trình tích hợp SoC, hiểu rõ bản chất của black-box macro cũng như các vấn đề liên quan đến LVS.

Mặc dù vẫn còn một số điểm có thể cải thiện như mô hình analog của PLL hoặc phân tích sâu hơn về timing, nhưng tổng thể dự án đã thể hiện tư duy hệ thống tốt và định hướng đúng với yêu cầu của ngành thiết kế vi mạch hiện đại.

Dự án “Design and SoC Integration of a PLL Macro in Caravel Platform” không chỉ là một đồ án học tập mà còn là minh chứng cho năng lực tiếp cận công nghệ thực tế của sinh viên FPT Jetking. Trong bối cảnh ngành bán dẫn đang phát triển mạnh, những trải nghiệm như vậy sẽ là nền tảng quan trọng giúp sinh viên sẵn sàng tham gia vào các dự án quy mô lớn và trở thành kỹ sư vi mạch trong tương lai.

Giảng viên Trương Huy Hoàng