Với mong muốn mang kiến thức Verilog áp dụng vào một hệ thống quen thuộc nhưng đầy thử thách, Nguyễn Vũ – sinh viên lớp C1.2503.E1 đã thực hiện đồ án “Verilog – Traffic Light mở rộng” trong học kỳ 2, khóa học Thiết kế Vi mạch tại FPT Jetking. Dự án là sự kết hợp giữa tư duy thiết kế mạch số, lập trình FSM (Finite State Machine), và khả năng giao tiếp ngoại vi với LCD, giúp mô phỏng chân thực hoạt động của hệ thống đèn giao thông tự động trên nền FPGA.

Từ ý tưởng quen thuộc đến ứng dụng thực tế

Đèn giao thông là một trong những hệ thống điều khiển phổ biến nhất trong đời sống hiện đại. Tuy nhiên, để tái hiện hoàn chỉnh nguyên lý hoạt động của nó trên nền tảng FPGA bằng ngôn ngữ mô tả phần cứng Verilog lại là một bài toán kỹ thuật thú vị và đầy thách thức.

Nguyễn Vũ chia sẻ rằng việc lựa chọn đề tài này không chỉ giúp hiểu sâu hơn về thiết kế mạch tuần tự và lập trình FSM, mà còn rèn luyện tư duy điều khiển logic theo thời gian thực – nền tảng quan trọng trong ngành thiết kế vi mạch. Đồ án còn được mở rộng với màn hình LCD 1602 để hiển thị trạng thái và thông báo, giúp mô hình trở nên sinh động và gần gũi với ứng dụng thực tế.

Mục tiêu và hướng triển khai

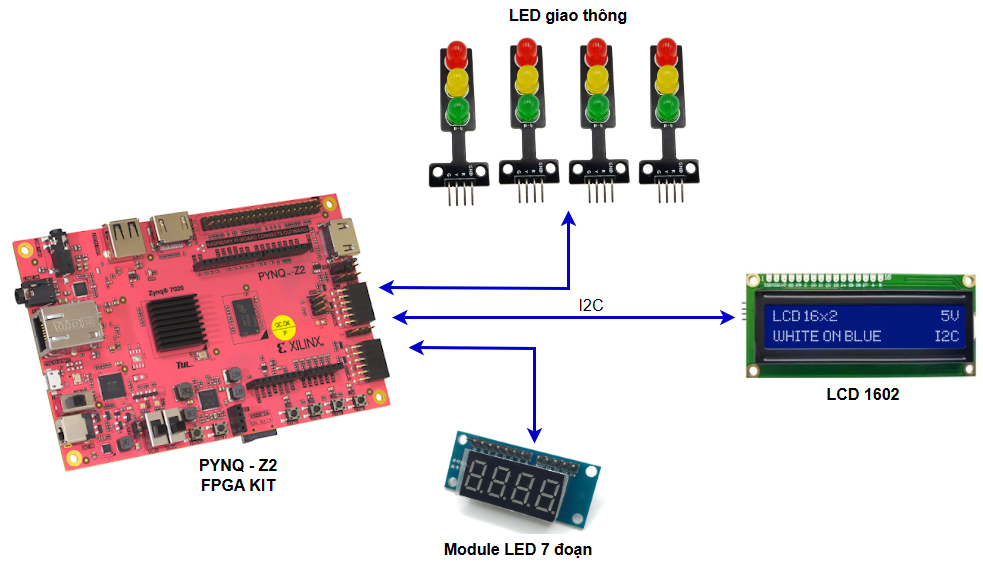

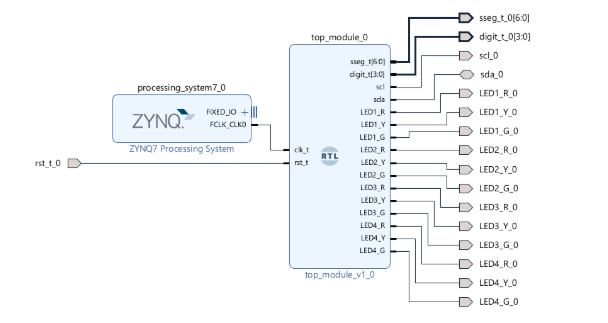

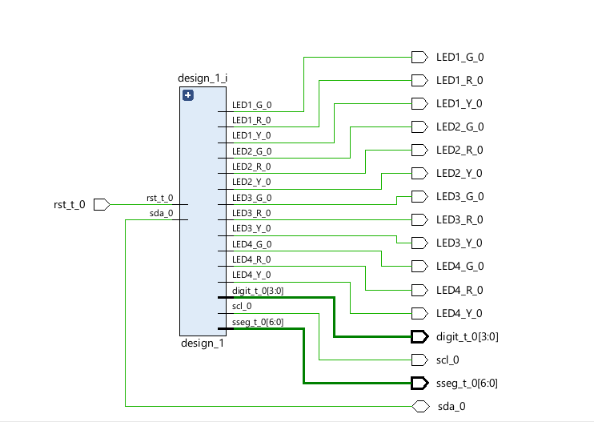

Mục tiêu của đồ án là thiết kế mô hình điều khiển đèn giao thông tự động, có khả năng hiển thị trạng thái đèn, thời gian đếm ngược và thông báo trên màn hình LCD. Sinh viên còn hướng tới mở rộng khả năng điều khiển song song nhiều cụm đèn hoạt động đồng bộ, qua đó mô phỏng hệ thống giao thông hoàn chỉnh.

Quá trình triển khai gồm nhiều giai đoạn liên kết chặt chẽ:

-

Phân tích và xác định các trạng thái hoạt động của hệ thống (RED, GREEN, YELLOW)

-

Thiết kế FSM điều khiển chu kỳ đèn bằng Verilog

-

Xây dựng module đếm thời gian (counter) tương ứng với từng pha đèn

-

Viết module điều khiển LCD 1602 để hiển thị thông tin qua bus dữ liệu

-

Tiến hành mô phỏng trên phần mềm Vivado, sau đó nạp và kiểm thử trên board FPGA Zynq-7020

-

Cuối cùng, sinh viên lắp ráp mạch LED mô phỏng đèn giao thông thực tế và hiệu chỉnh độ trễ hiển thị

Mô hình hoàn thiện có thể vận hành ổn định, hiển thị thời gian đếm ngược và thông báo tương ứng với từng trạng thái đèn, mang lại cảm giác điều khiển trực quan và thực tế.

Thử thách kỹ thuật và cách vượt qua

Một trong những thử thách lớn nhất của đồ án là giao tiếp với LCD 1602, vốn yêu cầu độ chính xác cao về thời gian và chuỗi lệnh khởi tạo. Chỉ cần sai lệch vài microsecond cũng có thể khiến LCD hiển thị ký tự lỗi hoặc không hoạt động.

Để giải quyết, Nguyễn Vũ đã nghiên cứu kỹ datasheet LCD, thiết kế một module điều khiển riêng (LCD_Controller.v) và sử dụng FSM con để quản lý trình tự lệnh hiển thị. Ngoài ra, anh còn thêm bộ chia xung (clock divider) nhằm đồng bộ hóa tín hiệu giữa các module đèn và bộ đếm, đảm bảo quá trình hiển thị ổn định trên màn hình.

Nhớ lại quá trình thử nghiệm, Nguyễn Vũ chia sẻ: “Có lần LCD hiển thị toàn ký tự lạ, nhóm phải ‘debug’ gần hai tiếng mới phát hiện lỗi timing chỉ vì chênh 40 microsecond. Nhưng khoảnh khắc dòng chữ ‘RED STOP!’ xuất hiện lần đầu trên LCD, cảm giác thật sự ‘phê’ – như nhìn thấy FPGA của mình biết nói.”

Hoàn thiện sản phẩm – Từ mô phỏng đến trải nghiệm trực quan

Sản phẩm hoàn thiện là một mô hình đèn giao thông mở rộng với giao diện LCD hiển thị thông minh. Màn hình hiện dòng chữ “JETKING GROUP 2 – RED STOP!” kèm thời gian đếm ngược, đồng thời hệ thống mô phỏng hai cụm đèn giao thông hoạt động đồng bộ như trong thực tế.

Ngoài LCD, dự án còn tích hợp bộ đếm LED 7 đoạn và LED báo trạng thái, giúp người xem dễ dàng quan sát hoạt động của từng pha đèn. Thiết kế được đánh giá có tính mở rộng cao, có thể dễ dàng bổ sung cảm biến hoặc nút nhấn điều khiển tay, hướng tới các hệ thống điều khiển giao thông thông minh hơn trong tương lai.

Bài học và giá trị đạt được sau dự án

Sau khi hoàn thành đồ án, Nguyễn Vũ đã nắm vững quy trình thiết kế FSM trong Verilog, hiểu rõ nguyên lý giao tiếp giữa FPGA và các thiết bị ngoại vi như LCD, LED và bộ đếm. Quan trọng hơn, sinh viên học được cách phân tích – thiết kế – kiểm thử – và debug trong môi trường phần cứng thực tế, đồng thời rèn luyện tinh thần kiên nhẫn và làm việc nhóm hiệu quả.

Dự án không chỉ giúp củng cố kiến thức học thuật mà còn mang lại trải nghiệm mô phỏng thực tế – yếu tố giúp sinh viên FPT Jetking sẵn sàng cho môi trường doanh nghiệp khi làm việc với các hệ thống nhúng và thiết kế vi mạch phức tạp.

Theo đánh giá của thầy Trương Huy Hoàng – giảng viên hướng dẫn trực tiếp, đây là một bài tập xuất sắc, thể hiện khả năng tư duy logic rõ ràng và năng lực triển khai thiết kế có tổ chức. Các module được xây dựng chặt chẽ, LCD hiển thị ổn định, mô hình thực tế trình bày gọn gàng và đẹp mắt.

Điểm cần hoàn thiện trong các phiên bản sau là bổ sung nút nhấn điều khiển tay hoặc cảm biến nhận diện phương tiện, đồng thời minh họa waveform mô phỏng để giúp người xem hiểu rõ hơn về quá trình hoạt động logic của hệ thống.

Dự án “Verilog – Traffic Light mở rộng” không chỉ là một bài tập học thuật mà còn là minh chứng cho khả năng làm chủ công nghệ FPGA của sinh viên FPT Jetking – nơi lý thuyết được biến thành sản phẩm thực tiễn, và từng dòng mã Verilog đều mang hơi thở của sáng tạo và đam mê kỹ thuật.

Giảng viên Trương Huy Hoàng