Trong lĩnh vực thiết kế vi mạch và hệ thống số, các khối tạo số ngẫu nhiên giữ vai trò nền tảng trong rất nhiều ứng dụng quan trọng như bảo mật, mã hóa, mô phỏng, trò chơi điện tử và hệ thống nhúng. Xuất phát từ yêu cầu đó, sinh viên FPT Jetking đã triển khai đồ án Verilog – Máy phát số ngẫu nhiên, một project thực hành tiêu biểu trong học kỳ 2 của khóa học Thiết kế vi mạch.

Đồ án không chỉ dừng lại ở việc mô phỏng thuật toán trên phần mềm, mà còn được hiện thực hóa trên phần cứng thật với nền tảng FPGA kết hợp IoT, thể hiện rõ định hướng đào tạo thực hành chuyên sâu tại FPT Jetking.

Thông tin tổng quan về đồ án Verilog – Máy phát số ngẫu nhiên

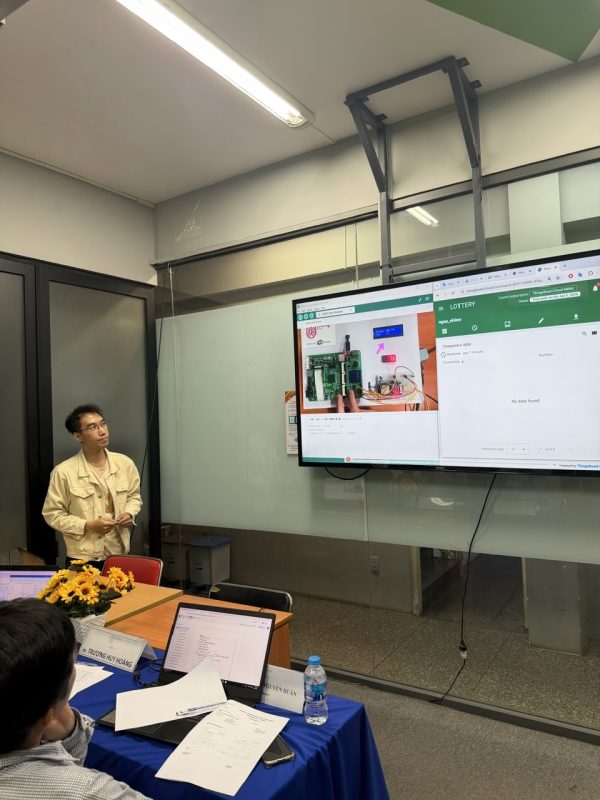

Dự án được thực hiện bởi sinh viên Vòng Kháng Hữu và Nguyễn Minh Thuận, lớp C1.2502.E0, trong khuôn khổ project cuối học kỳ 2 – khóa học Thiết kế vi mạch tại FPT Jetking. Đây là một trong những đồ án xuất sắc của học kỳ, thuộc nhóm sản phẩm thực hành FPGA kết hợp IoT.

Sản phẩm được xây dựng theo mô hình hệ thống hoàn chỉnh, bao gồm thiết kế RTL bằng Verilog, tích hợp giao tiếp LCD thông qua I2C và mở rộng khả năng truyền dữ liệu qua nền tảng IoT.

Hệ thống tạo số ngẫu nhiên là một khối chức năng cơ bản nhưng vô cùng quan trọng trong các hệ thống số hiện đại. Từ mã hóa dữ liệu, bảo mật thông tin cho đến mô phỏng và điều khiển nhúng, việc tạo ra chuỗi số ngẫu nhiên có độ tin cậy cao là yêu cầu bắt buộc.

Nhóm sinh viên lựa chọn đề tài này nhằm kết hợp đồng thời nhiều mảng kiến thức đã học, từ Verilog, FPGA, giao tiếp ngoại vi I2C, hiển thị LCD cho đến mở rộng sang IoT. Thông qua đó, nhóm mong muốn xây dựng một mô hình sát với ứng dụng công nghiệp, thay vì chỉ dừng lại ở các bài tập mô phỏng đơn lẻ.

Quá trình triển khai và xây dựng hệ thống

Ngay từ đầu, nhóm xác định mục tiêu chính là thiết kế và hiện thực một máy phát số ngẫu nhiên hoàn chỉnh bằng Verilog trên FPGA. Hệ thống không chỉ tạo ra chuỗi số pseudo-random, mà còn phải hiển thị kết quả trực tiếp trên LCD và truyền dữ liệu ra ngoài thông qua kết nối IoT.

Bên cạnh mục tiêu kỹ thuật, đồ án còn hướng đến việc giúp sinh viên làm chủ toàn bộ quy trình thiết kế, từ xây dựng RTL, mô phỏng, nạp chương trình lên FPGA cho đến kiểm thử trên phần cứng thật.

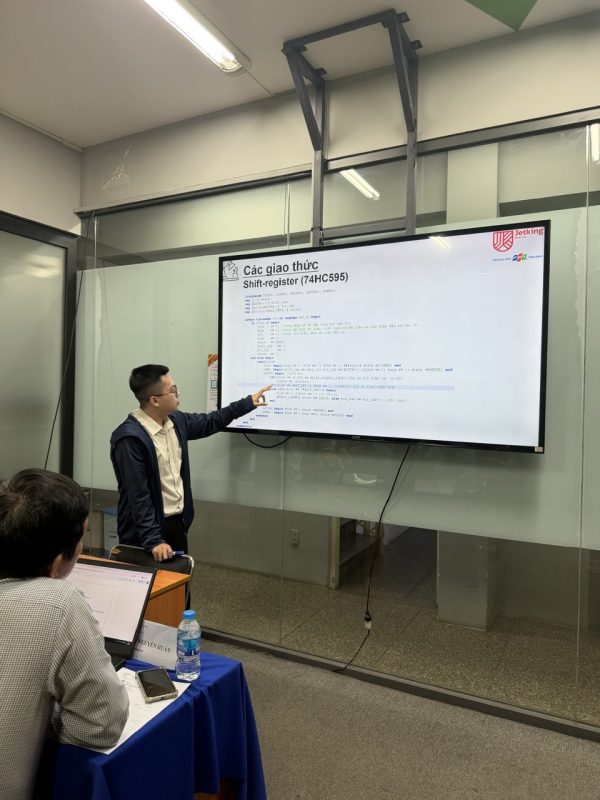

Dự án được bắt đầu bằng việc phân tích yêu cầu hệ thống và xây dựng sơ đồ khối tổng thể. Nhóm thiết kế thuật toán tạo số ngẫu nhiên dựa trên LFSR và logic pseudo-random bằng ngôn ngữ Verilog, sau đó xây dựng các module chức năng như timer, control, random generator và giao tiếp LCD thông qua I2C.

Mỗi module đều được mô phỏng và debug riêng lẻ trên phần mềm trước khi tích hợp toàn hệ thống trên FPGA board. Sau khi phần cứng hoạt động ổn định, nhóm tiến hành kết nối IoT và kiểm thử khả năng hiển thị cũng như truyền dữ liệu trong điều kiện thực tế.

Thử thách kỹ thuật và cách nhóm vượt qua

Một trong những khó khăn lớn nhất của dự án là việc đọc và phân tích tín hiệu I2C và LCD ở mức bit, nibble và timing, đòi hỏi độ chính xác rất cao. Bên cạnh đó, việc đồng bộ dữ liệu giữa nhiều module khác nhau trên FPGA cũng gây ra không ít lỗi trong giai đoạn đầu.

Để giải quyết, nhóm tập trung nghiên cứu kỹ datasheet của LCD, chuẩn I2C và waveform timing. Mỗi khối chức năng được mô phỏng độc lập trước khi tích hợp, đồng thời việc debug được thực hiện bằng cách quan sát waveform và test từng bước trên phần cứng thật.

Trong quá trình thực hiện, nhóm từng gặp tình huống hệ thống hiển thị sai giá trị trên LCD do nhầm thứ tự nibble trong giao tiếp I2C. Việc trace lại từng bit mất rất nhiều thời gian và công sức.

Khoảnh khắc hệ thống hiển thị đúng số ngẫu nhiên và cập nhật liên tục trên màn hình sau khi sửa lỗi đã trở thành một kỷ niệm đặc biệt, giúp cả nhóm cảm nhận rõ giá trị của sự kiên trì và tư duy debug hệ thống.

Điểm nổi bật của sản phẩm hoàn thiện

Sản phẩm hoàn chỉnh gây ấn tượng bởi giao diện LCD hiển thị rõ ràng, trực quan, thể hiện đầy đủ giá trị ngẫu nhiên và trạng thái hệ thống. Việc kết hợp FPGA với IoT cho thấy khả năng mở rộng của hệ thống sang các mô hình thông minh trong tương lai.

Thiết kế được xây dựng theo mô hình module hóa, giúp việc bảo trì, nâng cấp và phát triển thêm tính năng trở nên thuận lợi hơn.

Sau khi hoàn thành đồ án, sinh viên đã nắm vững quy trình thiết kế RTL bằng Verilog trên nền tảng FPGA. Kiến thức về giao tiếp I2C, điều khiển LCD, timing và debug hệ thống nhúng được củng cố rõ rệt thông qua trải nghiệm thực tế.

Bên cạnh đó, dự án còn giúp sinh viên rèn luyện kỹ năng làm việc nhóm, phân chia module hợp lý và tích hợp toàn hệ thống, những năng lực rất quan trọng đối với kỹ sư thiết kế số và hệ thống nhúng.

Một thành viên trong nhóm chia sẻ rằng: “Lần đầu triển khai một hệ thống hoàn chỉnh từ Verilog đến phần cứng thật đã giúp anh hiểu rõ hơn cách một thiết kế vi mạch và FPGA vận hành trong môi trường thực tế, thay vì chỉ dừng lại ở mô phỏng trên phần mềm”.

Đánh giá từ giảng viên hướng dẫn

Theo nhận xét của giảng viên, dự án có cấu trúc hệ thống rõ ràng, phân tách module hợp lý và tích hợp thành công giữa FPGA, LCD và IoT. Đây là minh chứng cho tư duy hệ thống tốt và năng lực thực hành vững vàng của sinh viên.

Bên cạnh đó, giảng viên cũng đề xuất nhóm có thể tối ưu thêm thuật toán tạo số ngẫu nhiên và bổ sung các chức năng như lưu log hoặc truyền dữ liệu lên cloud để nâng cao tính ứng dụng trong tương lai. Tổng thể, đây là một bài đồ án chất lượng, thể hiện tốt năng lực thực hành FPGA, thiết kế số và hệ thống nhúng của sinh viên FPT Jetking.

Đồ án Verilog – Máy phát số ngẫu nhiên là minh chứng rõ nét cho phương pháp đào tạo chuyên sâu về thiết kế vi mạch tại FPT Jetking. Thông qua các project thực hành từ mô phỏng đến phần cứng thật, sinh viên không chỉ học lý thuyết, mà còn từng bước làm chủ quy trình thiết kế hệ thống số trong môi trường gần với công nghiệp.

Những đồ án như vậy đang góp phần xây dựng thế hệ kỹ sư vi mạch trẻ, có nền tảng kỹ thuật vững vàng và sẵn sàng tham gia vào lĩnh vực thiết kế chip và hệ thống nhúng trong tương lai.

Cùng xem demo của nhóm qua video bên dưới nhé!

Giảng viên Trương Huy Hoàng