Trong học kỳ 2 của môn Exam & Project, nhóm 3 đã thực hiện thành công đồ án “Thiết kế và đánh giá mô-đun SPI bằng Verilog HDL”. Đây là một sản phẩm quan trọng không chỉ giúp sinh viên áp dụng kiến thức lý thuyết vào thực tế mà còn rèn luyện kỹ năng thiết kế, mô phỏng và kiểm chứng hệ thống số trên FPGA.

Lý do chọn đề tài

Đồ án được thực hiện bởi nhóm 3 gồm các thành viên Nguyễn Vũ Mạnh Bảo, Nguyễn Trường Trung và Trần Nguyễn Diễm Quỳnh. Với sự phối hợp ăn ý, nhóm đã hoàn thành một sản phẩm có tính ứng dụng cao, minh chứng cho khả năng kết hợp kiến thức lý thuyết với kỹ năng thực hành.

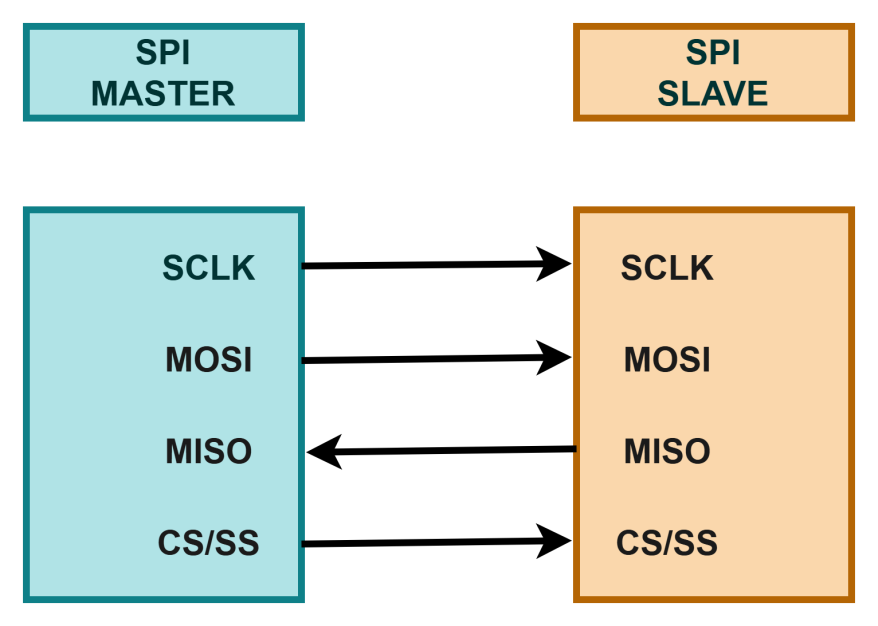

SPI là một trong những chuẩn giao tiếp ngoại vi phổ biến trong thiết kế vi mạch và hệ thống nhúng. Việc lựa chọn đề tài này giúp nhóm củng cố kiến thức về chuẩn SPI, rèn luyện kỹ năng lập trình trên FPGA, đồng thời hiểu rõ cơ chế hoạt động và kết nối giữa các bo mạch. Bên cạnh đó, dự án còn là cơ hội để nhóm tiếp cận quy trình triển khai một sản phẩm thực tế, quản lý tiến độ và đảm bảo chất lượng – những yếu tố quan trọng cho định hướng phát triển trong lĩnh vực thiết kế vi mạch.

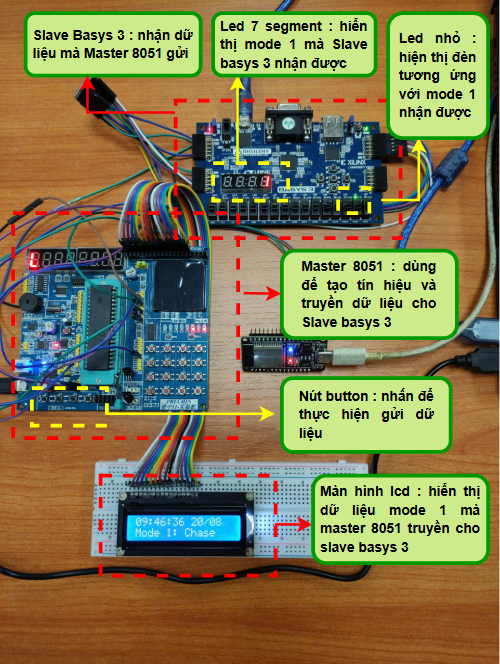

Đồ án hướng đến mục tiêu thiết kế và xây dựng mô-đun SPI bằng ngôn ngữ Verilog HDL, mô phỏng và kiểm tra hoạt động trên phần mềm Vivado, đồng thời triển khai trên phần cứng thực tế. Sản phẩm phải đảm bảo quá trình giao tiếp chính xác giữa kit 8051 đóng vai trò Master và kit Basys 3 đóng vai trò Slave. Dữ liệu được truyền từ 8051 sang Basys 3 và hiển thị rõ ràng trên LED, thể hiện đầy đủ các chế độ hoạt động. Ngoài ra, dự án còn giúp các thành viên rèn luyện kỹ năng thiết kế mạch số, mô phỏng và phân tích kết quả thực nghiệm.

Quy trình triển khai đồ án

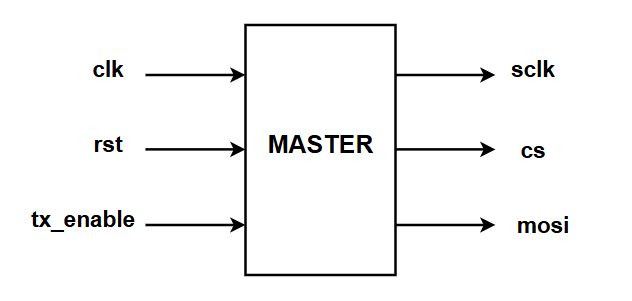

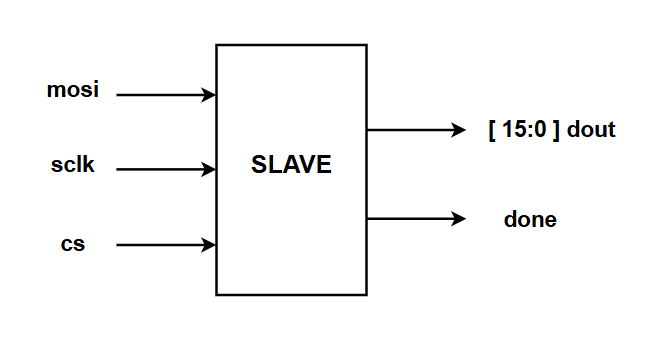

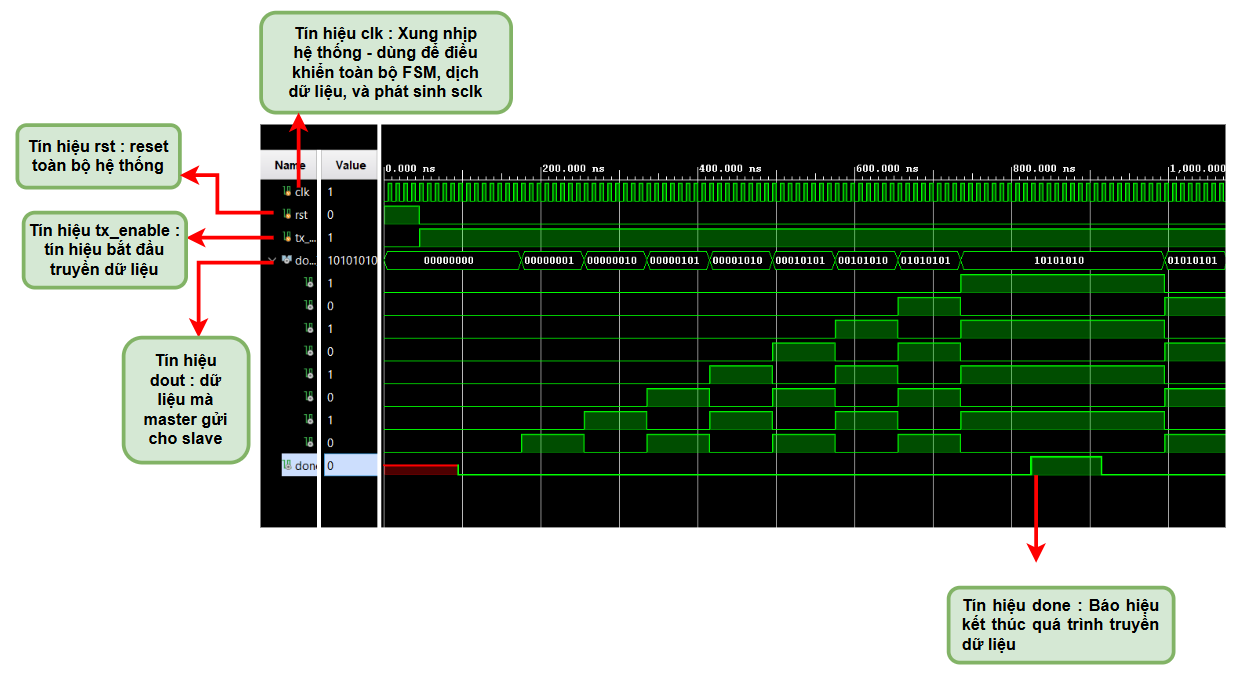

Nhóm bắt đầu bằng việc tìm hiểu lý thuyết cơ bản về chuẩn SPI, nắm vững nguyên lý hoạt động giữa Master và Slave. Sau đó, nhóm tiến hành xây dựng sơ đồ khối tổng thể, sơ đồ khối SPI Master và sơ đồ khối SPI Slave. Mạch được kiểm chứng bằng phần mềm Vivado. Khi tx_enable = 1, quá trình truyền dữ liệu từ master sang slave bắt đầu. Tín hiệu dout chứa dữ liệu cần truyền, sau khi hoàn tất thì tín hiệu done = 1 báo hiệu kết thúc truyền.

Ở giai đoạn triển khai trên phần cứng, Basys 3 được cấu hình làm Slave và kit 8051 làm Master. Các nút nhấn trên kit 8051 được sử dụng để chọn chế độ dữ liệu. Khi người dùng nhấn nút, dữ liệu được truyền sang Basys 3, hiển thị trên LED bảy đoạn và các LED đơn với hiệu ứng tương ứng.

Trong quá trình thực hiện, nhóm gặp thách thức lớn khi phát triển đầy đủ chức năng của SPI. Để vượt qua, các thành viên chia nhỏ công việc, bắt đầu từ những bước cơ bản rồi mở rộng sang các chức năng nâng cao. Nhờ vậy, tiến độ được kiểm soát và sản phẩm dần hoàn thiện.

Mặc dù có nhiều khó khăn về kỹ thuật, nhưng đây cũng là cơ hội để nhóm gắn kết hơn. Các thành viên nhận ra điểm mạnh của nhau để phân công hợp lý, từ đó nâng cao hiệu quả làm việc chung. Khoảnh khắc sản phẩm chạy đúng như mô phỏng và hiển thị chính xác trên kit FPGA là niềm vui lớn nhất, tạo động lực để nhóm tiếp tục theo đuổi lĩnh vực kỹ thuật số.

Điểm nổi bật của đồ án

Đồ án hoàn thiện với khả năng truyền dữ liệu chính xác giữa Master và Slave, hiển thị đầy đủ các chế độ và hiệu ứng LED. Kết quả mô phỏng và thử nghiệm thực tế trùng khớp, đảm bảo tính ổn định và độ tin cậy. Thiết kế có khả năng mở rộng và ứng dụng trong nhiều bài toán thực tiễn khác. Đây cũng là bước phát triển cao hơn từ đồ án kỳ trước, thể hiện tính ứng dụng rõ rệt của chuẩn SPI trong thiết kế vi mạch.

Qua dự án, các thành viên đã nắm chắc hơn về quy trình xây dựng sản phẩm vi mạch từ lập kế hoạch, thiết kế, mô phỏng đến kiểm chứng thực nghiệm. Kiến thức về Verilog HDL và FPGA được củng cố vững vàng, đồng thời kỹ năng làm việc nhóm và quản lý dự án cũng được nâng cao đáng kể.

Nguyễn Vũ Mạnh Bảo chia sẻ “Việc tích hợp ba nền tảng riêng biệt thông qua SPI là một thách thức nhưng vô cùng bổ ích. Hệ thống hiện chứng minh được khả năng giao tiếp mạnh mẽ, độ trễ thấp và cung cấp một nền tảng linh hoạt cho các cải tiến trong tương lai.”

Nguyễn Trường Trung cũng cho biết “Qua dự án này, em thực sự thấu hiểu rằng sức mạnh của một hệ thống phức tạp không nằm ở từng linh kiện riêng lẻ, mà ở nghệ thuật kết nối chúng lại để giao tiếp một cách hài hòa. Việc tích hợp thành công vi điều khiển 8051, module ESP32 và mạch FPGA đã mang lại cho em một cảm giác hoàn thành tuyệt vời và một bài học vô giá về kỹ thuật tích hợp hệ thống.”

Trần Nguyễn Diễm Quỳnh nhận xét dự án giúp cô có cái nhìn thú vị khi thấy rằng giao tiếp giữa các bo mạch cũng giống như giao tiếp giữa con người, đều cần có ngôn ngữ và tín hiệu để thấu hiểu lẫn nhau.

Thầy Lộc – giảng viên hướng dẫn đánh giá sản phẩm có nhiều ưu điểm nổi bật như hoạt động ổn định, triển khai đúng chức năng, áp dụng tốt lý thuyết vào thực tế và xây dựng được đầy đủ giao thức SPI. Nhóm được ghi nhận đã làm việc nghiêm túc, hoàn thành mục tiêu đề ra và thể hiện sự tiến bộ rõ rệt trong cả tinh thần lẫn hiệu quả hoạt động tập thể.

Đồ án “Thiết kế và đánh giá mô-đun SPI bằng Verilog HDL” không chỉ là một bài tập học thuật mà còn là bước khởi đầu quan trọng để sinh viên nhóm 3 tiếp cận gần hơn với thực tiễn ngành thiết kế vi mạch. Sản phẩm thể hiện rõ khả năng ứng dụng của chuẩn SPI, đồng thời khẳng định năng lực và sự sáng tạo của sinh viên FPT Jetking trong việc đưa kiến thức lý thuyết vào sản phẩm thực tế.

Giảng viên Nguyễn Văn Thành Lộc