Trong bối cảnh ngành công nghiệp bán dẫn bùng nổ, sinh viên Học viện thiết kế vi mạch bán dẫn FPT Jetking tiếp tục khẳng định năng lực hội nhập toàn cầu thông qua các dự án chip thực tế. Điển hình là đồ án “Hệ thống AES Accelerator” do sinh viên Võ Nhật Trường và các thành viên nhóm gồm Đặng Hữu Thái Hòa, Trần Ngọc Thắng Nguyễn Bách Thông, Nguyễn Chí Tâm đã bảo vệ thành công và có khả năng phát hành trên hệ sinh thái mã nguồn mở OSEDA. Đây được xem là bước tiến quan trọng, mở ra kỷ nguyên mới cho đào tạo nhân lực công nghệ cao trong lĩnh vực thiết kế và chế tạo vi mạch tại Việt Nam.

Hành trình triển khai đồ án AES – từ ý tưởng đến sản phẩm chip thực tế

Vừa qua, tại FPT Jetking cơ sở 21 Bis Hậu Giang, sinh viên lớp C1.2405.E0 đã tham gia bảo vệ đồ án cuối kỳ 3 học phần “Thiết kế chip từ ý tưởng đến sản phẩm thực tế”. Đây là học phần đặc biệt khi sinh viên được tiếp cận toàn bộ quy trình thiết kế chip chuẩn quốc tế, từ giai đoạn RTL cho tới phát hành dữ liệu chế tạo GDSII trên nền tảng Caravel SoC do Google và Efabless phát triển.

Điểm khác biệt của học phần này nằm ở việc sinh viên không chỉ học lý thuyết mà còn trực tiếp tham gia thiết kế, mô phỏng, kiểm thử và phát hành sản phẩm chip thực tế. Sản phẩm cuối kỳ không dừng lại ở mô phỏng mà có khả năng tích hợp và đặt hàng chế tạo trên các foundry quốc tế như Skywater Foundry.

Đồ án AES Accelerator – tiêu chuẩn mã hóa quốc tế

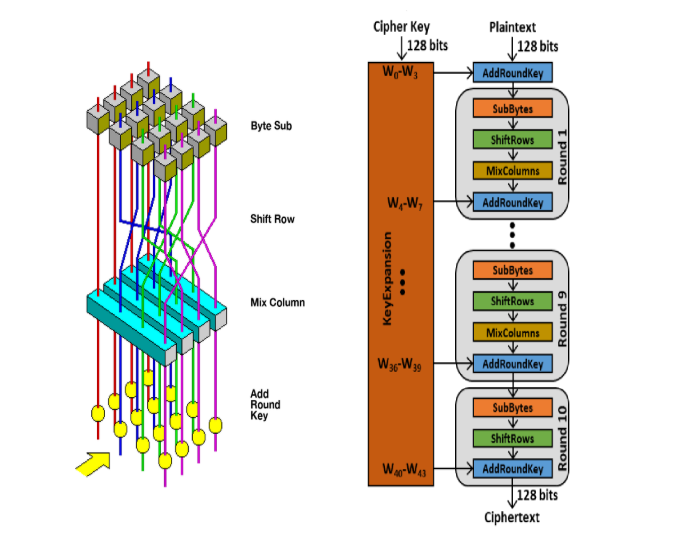

Với sự hướng dẫn từ giảng viên, nhóm sinh viên Võ Nhật Trường đã lựa chọn đề tài thiết kế chip AES Accelerator – bộ mã hóa tiên tiến theo chuẩn quốc tế AES (Advanced Encryption Standard). AES nổi bật nhờ cấu trúc toán học hiện đại, hỗ trợ độ dài khóa linh hoạt 128, 192 và 256 bit, tốc độ xử lý nhanh và khả năng triển khai hiệu quả trên cả phần cứng lẫn phần mềm.

Khác với DES/3DES truyền thống, AES được chuẩn hóa và công khai rộng rãi, nhờ vậy trở thành thuật toán mã hóa toàn cầu, ứng dụng trong nhiều lĩnh vực từ bảo mật dữ liệu, viễn thông, Internet đến các hệ thống nhúng.

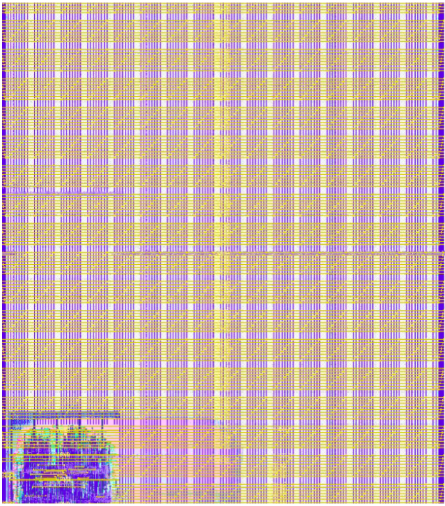

Trong đồ án, nhóm sinh viên đã triển khai AES Accelerator trên công nghệ Skywater 130nm PDK với hệ sinh thái OSEDA. Từ việc xây dựng RTL, thiết kế kiến trúc AES IP Core, đến kiểm thử theo chuẩn NIST, nhóm đã hoàn thiện toàn bộ luồng thiết kế chuẩn quốc tế.

Đặc điểm AES Accelerator:

AES có những đặc điểm khác biệt so với DES/3DES:

- Độ dài khóa linh hoạt: hỗ trợ 128, 192 và 256 bit (so với DES chỉ có 56 bit).

- Khối dữ liệu 128 bit (DES chỉ 64 bit).

- Cấu trúc toán học hiện đại: dùng các phép biến đổi trong đại số hữu hạn (S-box, ShiftRows, MixColumns).

- Nhanh và hiệu quả: AES được thiết kế để chạy tốt trên cả phần cứng và phần mềm.

- Tính chuẩn hóa quốc tế: không thuộc sở hữu riêng, được công khai thuật toán và khuyến khích kiểm tra.

AES là chuẩn mã hóa quốc tế đầu tiên được chọn qua một cuộc thi mở, có sự đóng góp và đánh giá của cộng đồng học thuật, thay vì chỉ do chính phủ Mỹ tự chọn. Điều này giúp AES được tin tưởng rộng rãi.

Hệ thống OSEDA và PDK130nm được sự hỗ trợ mạnh mẽ từ Google, Skywater, Cadence, … và Trường Đại học khắp thế giới. Mong muốn thể hiện từ ý tưởng thiết kế đến việc chế tạo ra chip được dễ dàng và hiện thực nhất.

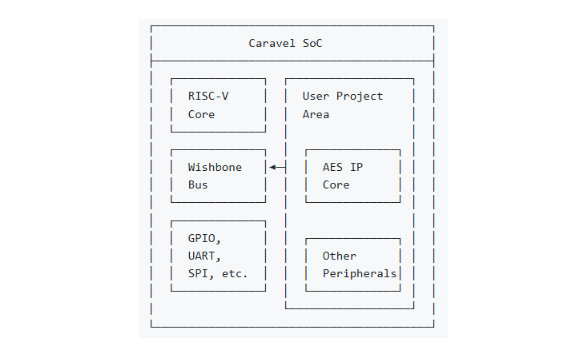

Lộ trình triển khai trên Caravel Platform và AES IP Core

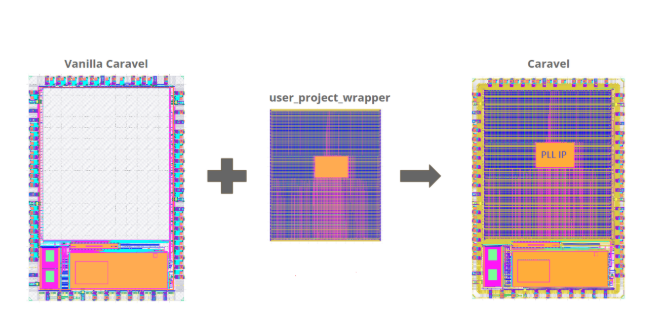

Caravel là một SoC (System-on-Chip) mã nguồn mở được phát triển bởi Google và Efabless, được thiết kế đặc biệt cho các dự án chip mã nguồn mở. Caravel cung cấp một nền tảng hoàn chỉnh để tích hợp các IP core tùy chỉnh.

Đặc điểm chính:

- Open Source: Toàn bộ RTL và tài liệu đều mở

- SkyWater 130nm: Sử dụng công nghệ SkyWater 130nm

- Wishbone Bus: Giao diện bus Wishbone chuẩn

- RISC-V Core: Tích hợp lõi RISC-V

- User Project Area: Khu vực dành cho IP core tùy chỉnh

Tích hợp AES IP Core

Giao Diện Wishbone

AES IP core được tích hợp thông qua giao diện Wishbone:

- Slave Interface: Nhận lệnh từ RISC-V core

- Register Map: Định nghĩa các thanh ghi điều khiển

- Data Transfer: Truyền dữ liệu và khóa

Memory Maping

0x3000_0000 – 0x3000_0003: Control Register

0x3000_0004 – 0x3000_0007: Status Register

0x3000_0008 – 0x3000_000B: Configuration Register

0x3000_0010 – 0x3000_002F: Key Storage (128-bit)

0x3000_0020 – 0x3000_002F: Input Block (128-bit)

0x3000_0030 – 0x3000_003F: Output Block (128-bit)

Điều khiển và trạng thái

- Control Register: Khởi tạo, bắt đầu mã hóa/giải mã

- Status Register: ready, finish, error

- Configuration Register: Chế độ mã hóa/giải mã, kích thước khóa

Lợi ích của Caravel Platform

Phát triển nhanh

- Pre-built Infrastructure: Hạ tầng có sẵn

- Standard Interfaces: Giao diện chuẩn

- Open Source Tools: Công cụ mở

Chi phí thấp

- No Licensing Fees: Không phí cấp phép

- Community Support: Hỗ trợ cộng đồng

- Shared Resources: Chia sẻ tài nguyên

Tương thích

- Industry Standards: Tiêu chuẩn công nghiệp

- Multiple Foundries: Nhiều nhà máy sản xuất

- Scalable Design: Thiết kế có thể mở rộng

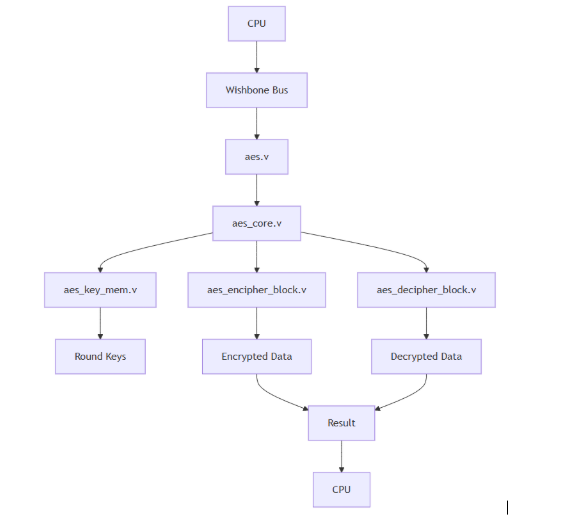

Nhóm khởi đầu bằng việc thiết kế HDL mô tả kiến trúc RTL của AES Accelerator, bao gồm các module chính và luồng thực thi CPU cần thiết để giao tiếp với AES core qua Wishbone protocol.

Kiến trúc tổng thể

aes.v (Top-Level)

├── aes_core.v (Control Logic)

├── aes_key_mem.v (Key Management)

├── aes_encipher_block.v (Encryption)

├── aes_decipher_block.v (Decryption)

├── aes_sbox.v (S-box Lookup)

└── aes_inv_sbox.v (Inverse S-box)

Quy trình nhúng thiết kế vào hệ sinh thái Caravel SoC:

Không chỉ dừng lại ở việc thiết kế một module riêng lẽ. Nhóm đã tận dụng nền tản Caravel để thiết kế thành một con chip SoC cho riêng mình.

Caravel là một SoC (System-on-Chip) mã nguồn mở được phát triển bởi Google và Efabless, được thiết kế đặc biệt cho các dự án chip mã nguồn mở. Caravel cung cấp một nền tảng hoàn chỉnh để tích hợp các IP core tùy chỉnh. Nhóm thiết kế đã tận dụng nền tảng SoC Caravel để đưa thiết kế mã hóa AES vào giúp giảm thời gian và công sức tiến tới đặt hàng chế tạo chip. Khai thác triệt để hệ thống BUS dùng trong thiết kế SoC, giúp kết nối các IP core hiệu quả, thống nhất và dễ tích hợp.

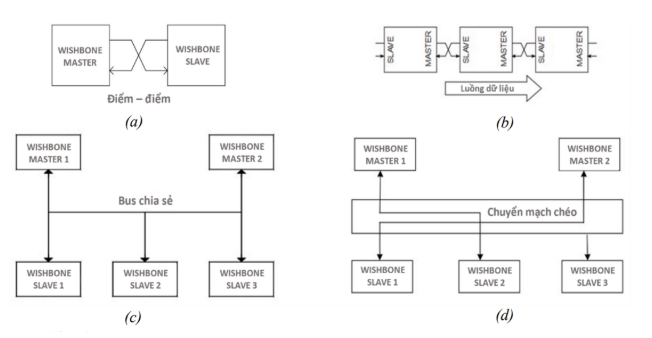

WISHBONE BUS là một hướng nghiên cứu mở rộng phục vụ cho chip mã hóa AES kết nối với CPU. Wishbone là BUS mã nguồn mở (do OpenCores phát triên) bên cạnh các kiến trúc BUS phổ biến khác như Họ AMBA (APB, AHP, AXI ) của ARM, Avalon của Intel FPGA, OPB của IBM.

Wishbone Bus có nhiều cấu hình liên kết linh hoạt: point-to-point, shared bus, data flow, crossbar switch.

Những tính năng nổi bật nhóm đã xây dựng chipset AES:

Chức Năng Chính

- End-to-End Testing: Kiểm tra toàn bộ flow từ input đến output

- NIST Compliance: Verify theo chuẩn NIST AES

- Multi-Mode Support: Test cả encryption và decryption

- Key Length Support: Hỗ trợ AES-128 và AES-256

- ECB Mode: Electronic Codebook mode testing

- Integration Testing: Kiểm tra tích hợp các module con

Phạm Vi Testing

- AES-128: Encryption/Decryption với 128-bit key

- AES-256: Encryption/Decryption với 256-bit key

- NIST Test Vectors: Sử dụng test cases chuẩn

- Error Handling: Kiểm tra xử lý lỗi

- Performance: Đo thời gian xử lý

Một điểm nổi bật của đồ án là việc tích hợp AES Accelerator vào Caravel SoC – nền tảng mã nguồn mở tích hợp lõi RISC-V và giao diện Wishbone. Nhờ đó, AES IP Core có thể kết nối trực tiếp với CPU và hệ thống ngoại vi, mở ra khả năng ứng dụng rộng rãi trong các hệ thống bảo mật, viễn thông và IoT.

Caravel cung cấp môi trường hoàn chỉnh cho việc nhúng IP Core, từ đó giảm thời gian thiết kế và tối ưu chi phí. Nhóm sinh viên đã tận dụng triệt để nền tảng này, tiến hành mapping bộ nhớ, xây dựng thanh ghi điều khiển, kiểm tra trạng thái và thực hiện mô phỏng end-to-end với dữ liệu thực tế.

Trong quá trình triển khai, nhóm sinh viên phải vượt qua nhiều thử thách khi xử lý các sơ đồ mạch phức tạp, mô phỏng luồng dữ liệu AES, đồng thời bảo đảm tính chuẩn hóa quốc tế của thuật toán. Tuy nhiên, nhờ tinh thần học như làm, cùng sự hướng dẫn từ giảng viên, nhóm đã hoàn thành đồ án với sản phẩm chip AES có khả năng phát hành chế tạo thực tế.

Sinh viên Võ Nhật Trường chia sẻ rằng việc trực tiếp thiết kế và kiểm thử AES Accelerator giúp nhóm hiểu rõ quy trình thiết kế chip quốc tế, đồng thời rèn luyện kỹ năng xử lý bài toán thực tế, từ mô phỏng HDL đến layout GDSII. Đây chính là hành trang quan trọng để sinh viên tự tin bước vào ngành công nghiệp bán dẫn.

Ý nghĩa và định hướng phát triển trong tương lai

Đồ án AES Accelerator không chỉ là một sản phẩm học tập mà còn mang ý nghĩa thực tiễn, minh chứng cho mô hình đào tạo gắn liền với doanh nghiệp và cộng đồng mã nguồn mở toàn cầu của FPT Jetking.

Trong tương lai, nhóm mong muốn mở rộng tính năng AES với các cơ chế bảo mật nâng cao, tối ưu hiệu suất và triển khai thực nghiệm trên FPGA cũng như ASIC. Những định hướng này sẽ giúp sản phẩm hoàn thiện hơn và có khả năng ứng dụng rộng rãi trong công nghiệp vi mạch và hệ thống nhúng.

Với thành công của đồ án AES Accelerator, sinh viên FPT Jetking đã cho thấy năng lực thiết kế chip ở mức độ quốc tế ngay từ khi còn ngồi trên ghế nhà trường. Việc sở hữu một sản phẩm chip hoàn chỉnh trong portfolio là lợi thế lớn, giúp sinh viên tự tin hội nhập và tham gia vào các dự án bán dẫn toàn cầu.

Video demo đồ án:

Giảng viên Nguyễn Ngọc Tiền