Trong bối cảnh ngành công nghiệp bán dẫn bùng nổ trên toàn thế giới, sinh viên học viện thiết kế vi mạch bán dẫn FPT Jetking đã và đang chứng minh năng lực hội nhập toàn cầu của mình thông qua những dự án chip thực tế. Điển hình là nhóm sinh viên Thái Gia Hưng và Trần Mạnh Quỳnh đã phát triển thành công sản phẩm thiết kế vi mạch PLL (Phase-Locked Loop – Vòng khóa pha). Đặc biệt, sản phẩm này không chỉ dừng ở mức mô phỏng mà còn có thể đặt hàng chế tạo thực tế trên các hệ sinh thái mã nguồn mở OSEDA (Open Source Electronic Design Automation), mở ra kỷ nguyên mới cho đào tạo nhân lực công nghệ cao tại Việt Nam.

Hành trình phát triển đồ án PLL – Từ ý tưởng đến sản phẩm chip thực

Vừa qua, tại FPT Jetking, các sinh viên khóa C1.2405.E0 đã tham gia bảo vệ đồ án học kỳ 3 thuộc môn học “Thiết kế chip từ ý tưởng đến sản phẩm thực tế”. Đây là học phần đặc biệt khi sinh viên được tiếp cận quy trình thiết kế chip chuẩn quốc tế theo nền tảng Caravel SoC – hệ sinh thái mã nguồn mở do Google và Efabless phát triển.

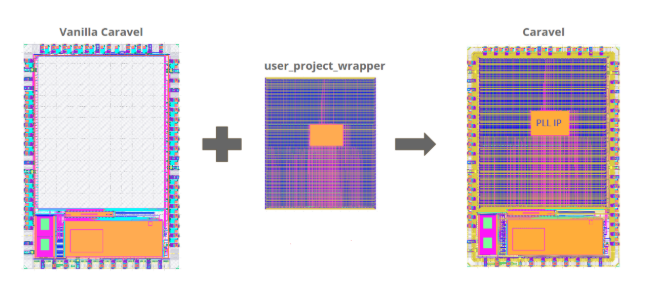

Điểm khác biệt nổi bật của học phần này là sinh viên không chỉ học lý thuyết mà trực tiếp thiết kế, mô phỏng, kiểm thử và phát hành chip thực tế. Sản phẩm cuối kỳ không dừng lại ở mô phỏng trên phần mềm, mà có khả năng tích hợp và đặt hàng chế tạo trên các foundry quốc tế như Skywater Foundry.

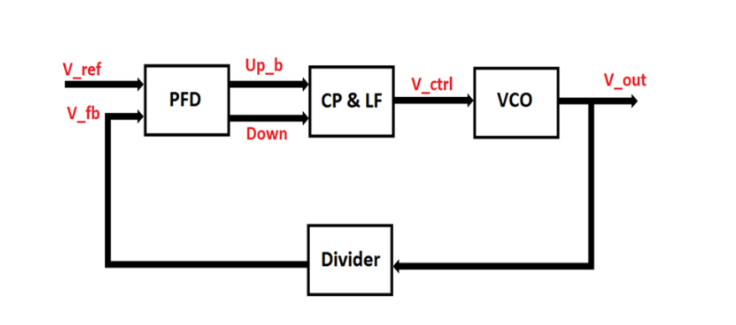

Trong dự án, nhóm sinh viên đã lựa chọn thiết kế PLL Clock Multiplier, một mạch nhân tần số clock đóng vai trò quan trọng trong các hệ thống điện tử số hiện đại, đặc biệt là SoC (System-on-Chip). PLL cho phép nhân tần số, đồng bộ pha và giảm jitter, từ đó tạo ra tín hiệu xung clock ổn định cho CPU, bộ nhớ, giao tiếp tốc độ cao hay hệ thống truyền thông.

Đồ án được triển khai trên công nghệ Skywater 130nm PDK với quy trình:

Khởi đầu từ việc xác định nhu cầu sử dụng PLL và các chức năng thiết yếu của mạch PLL. Nhóm triển khai từ việc xây dựng sơ đồ khối cho mạch PLL

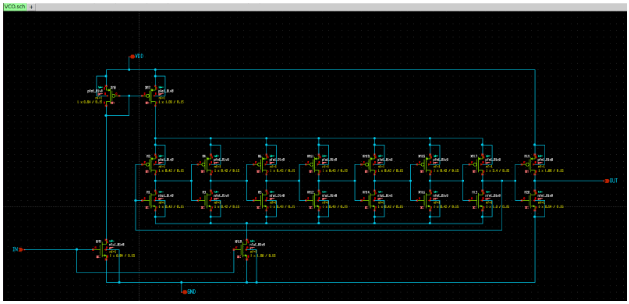

Nhóm chia vai trò thiết kế sơ đồ mạch từng khối riêng rồi tổng hợp lại trên nền tản phần mềm XSCHEM, NGSPICE mã nguồn mở.

Đồ án trải qua nhiều bước thiết kế, mô phỏng thực tế như mô phỏng tính năng từng khối từ mạch CMOS đã thiết kế, kiểm tra độ ổn định của tín hiệu, kết nối các khối lại thành tính năng PLL.

Một trong những thử thách lớn nhất nhóm gặp phải không chỉ là những sơ đồ mạch điện phức tạp, mà là khoảng cách giữa lý thuyết và thực tế. Với sự nổ lực tìm tòi và gợi ý của thầy lại là nguồn động lực giúp nhóm hoàn thiện và bảo vệ thành công dự án.

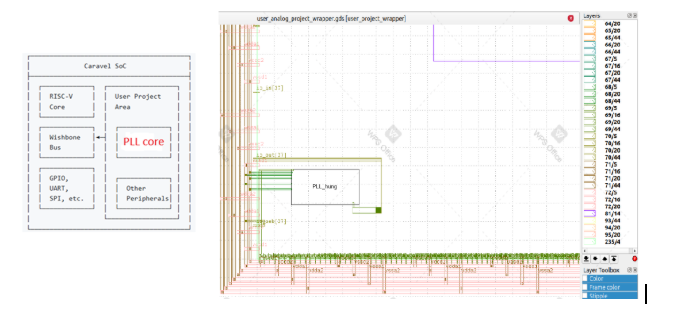

Quy trình nhúng thiết kế vào hệ sinh thái Caravel SoC:

Không chỉ dừng lại ở việc thiết kế một module riêng lẽ. Nhóm đã tận dụng nền tản Caravel để thiết kế thành một con chip SoC cho riêng mình.

Caravel là một SoC (System-on-Chip) mã nguồn mở được phát triển bởi Google và Efabless, được thiết kế đặc biệt cho các dự án chip mã nguồn mở. Caravel cung cấp một nền tảng hoàn chỉnh để tích hợp các IP core tùy chỉnh. Nhóm thiết kế sinh viên Hưng đã tận dụng nền tảng SoC Caravel để đưa thiết kế PLL vào giúp giảm thời gian và công sức tiến tới đặt hàng chế tạo chip.

Ứng dụng rộng rãi của PLL trong công nghiệp bán dẫn

Thiết kế PLL thành công mở ra nhiều ứng dụng quan trọng trong thực tiễn:

-

Vi xử lý và SoC: Intel, AMD, ARM SoC đều dùng PLL để nhân tần số clock từ MHz lên GHz

-

Bộ nhớ DDR/SDRAM: PLL đồng bộ dữ liệu tốc độ cao giữa CPU và DRAM

-

Chuẩn giao tiếp tốc độ cao: PCI Express, USB, HDMI, Ethernet đều dựa vào PLL để phục hồi và tạo clock

-

Truyền thông không dây: Wi-Fi, 4G/5G, GPS, Bluetooth dùng PLL trong bộ tổng hợp tần số

-

FPGA và vi điều khiển: PLL được tích hợp để nhân/giảm tần số phục vụ các ứng dụng nhúng

Những tính năng nổi bật của chipset PLL và ứng dụng trong các hệ thống điện tử:

- Vi xử lý & SoC hiện đại: Intel, AMD CPU mỗi nhân CPU đều có PLL riêng để nhân tần số clock từ vài chục MHz của thạch anh lên hàng GHz. Ví dụ, Intel Core i7 nhận clock tham chiếu ~100 MHz, PLL nhân lên thành 3–5 GHz.

- ARM-based SoC (Qualcomm Snapdragon, Apple A-series, Samsung Exynos): dùng nhiều PLL để cấp clock riêng cho CPU, GPU, DSP, bộ nhớ và ngoại vi. Ví dụ: trong chipset Qualcomm X55 5G, PLL nội bộ điều khiển VCO để tạo ra sóng mang từ vài trăm MHz đến hàng GHz.

- Bộ nhớ tốc độ cao: DDR, DDR2/3/4/5 SDRAM: PLL được tích hợp trong chip DRAM để nhân clock từ bộ điều khiển bộ nhớ, đồng bộ dữ liệu đọc/ghi.

- Chuẩn giao tiếp tốc độ cao: PCI Express, SATA, USB 3.x, HDMI, Ethernet (1G/10G/100G): đều dùng PLL để phục hồi clock (Clock Data Recovery – CDR) và tạo tín hiệu tốc độ cao từ clock gốc.

- Hệ thống RF và truyền thông không dây: Wi-Fi, 4G/5G, Bluetooth, GPS: PLL tạo tần số sóng mang trong bộ tổng hợp tần số (Frequency Synthesizer).

- Hệ thống nhúng và FPGA: FPGA (Xilinx, Intel/Altera, Lattice): tích hợp PLL để nhân/giảm/chia clock theo nhu cầu thiết kế.

- Microcontroller (STM32, PIC, Atmel AVR, ESP32): thường có PLL để nhân tần số từ thạch anh 8–16 MHz thành vài chục hoặc vài trăm MHz cho CPU core.

Thử thách và trải nghiệm đáng nhớ

Trong quá trình triển khai, thách thức lớn nhất của nhóm là khoảng cách giữa lý thuyết và thực tế, đặc biệt khi mô phỏng các mạch CMOS phức tạp. Tuy nhiên, nhờ sự kiên trì nghiên cứu tài liệu quốc tế và sự hướng dẫn tận tình từ giảng viên, nhóm đã khắc phục khó khăn, hoàn thiện và bảo vệ thành công sản phẩm.

Sinh viên Thái Gia Hưng chia sẻ: “Đồ án PLL giúp em hiểu rõ quy trình thiết kế chip chuẩn quốc tế, từ khâu ý tưởng đến phát hành GDSII. Đây là bước đệm quan trọng để em theo đuổi ngành bán dẫn ở mức độ chuyên sâu hơn.”

Thầy Nguyễn Ngọc Tiền – giảng viên hướng dẫn, nhận xét: “Đây là một đồ án bài bản, bám sát nhu cầu thực tế của ngành công nghiệp bán dẫn. Sinh viên đã thể hiện tinh thần tự học cao, khả năng vận dụng kiến thức nhanh chóng để tạo ra một sản phẩm vi mạch có giá trị ứng dụng thực sự. Đồ án PLL chính là minh chứng cho việc FPT Jetking đào tạo gắn liền với doanh nghiệp và cộng đồng mã nguồn mở toàn cầu.”

Bước đệm để hội nhập ngành bán dẫn quốc tế

Dự án PLL Clock Multiplier của sinh viên FPT Jetking không chỉ khẳng định năng lực đào tạo gắn với thực tế mà còn mở ra cơ hội hội nhập toàn cầu cho sinh viên ngành thiết kế vi mạch tại Việt Nam. Việc sở hữu một sản phẩm chip hoàn chỉnh ngay trong quá trình học tập giúp sinh viên có portfolio chuyên nghiệp, sẵn sàng tham gia vào các dự án quốc tế và bước chân vào ngành công nghiệp bán dẫn với sự tự tin cao nhất.

Đây chính là minh chứng rõ nét cho mô hình đào tạo “học như làm, làm như học” mà FPT Jetking đang tiên phong triển khai, góp phần đưa thế hệ kỹ sư bán dẫn Việt Nam tiến gần hơn với chuẩn mực toàn cầu.

Video Demo đồ án:

Giảng viên Nguyễn Ngọc Tiền