Công cụ Synthesis đóng vai trò then chốt, là cầu nối giữa ý tưởng thiết kế trên giấy và sản phẩm chip thực tế. Quy trình này đảm nhiệm vai trò tối ưu hóa thiết kế nhằm đạt được hiệu quả cao nhất về mặt timing, diện tích chip và mức tiêu thụ năng lượng. Nhờ đó, Synthesis góp phần tạo nên những vi mạch nhỏ gọn, hiệu quả và tiết kiệm điện năng, đáp ứng nhu cầu ngày càng cao của thị trường công nghệ hiện đại. Bài viết này FPT Jetking sẽ giới thiệu về khái niệm, chức năng, điểm nổi bật, vai trò Synthesis.

Công cụ Synthesis là gì?

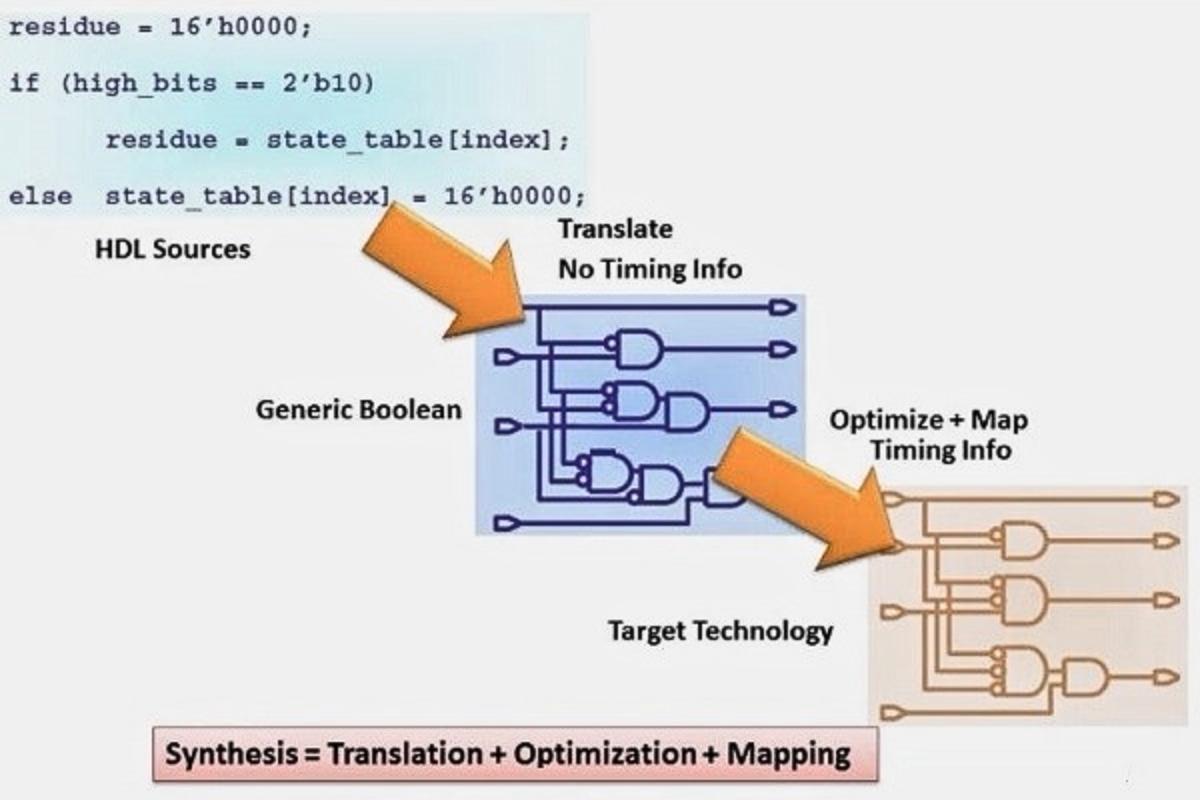

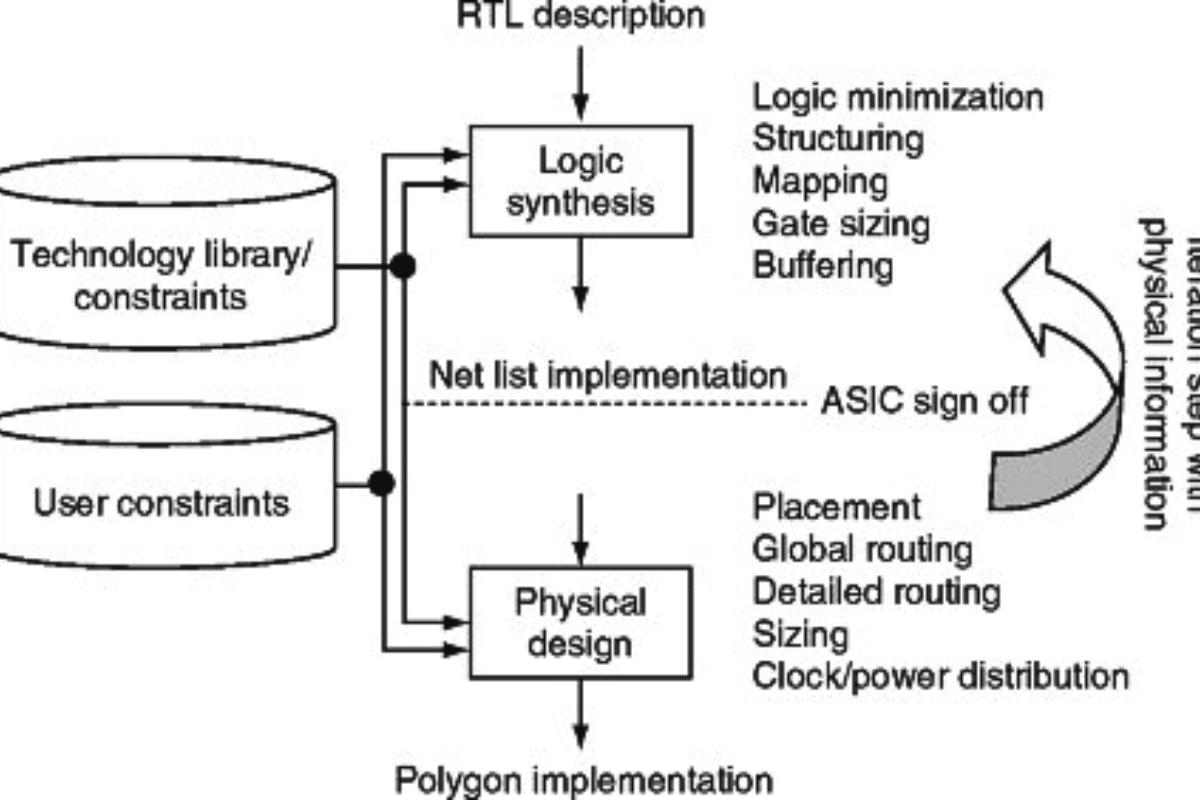

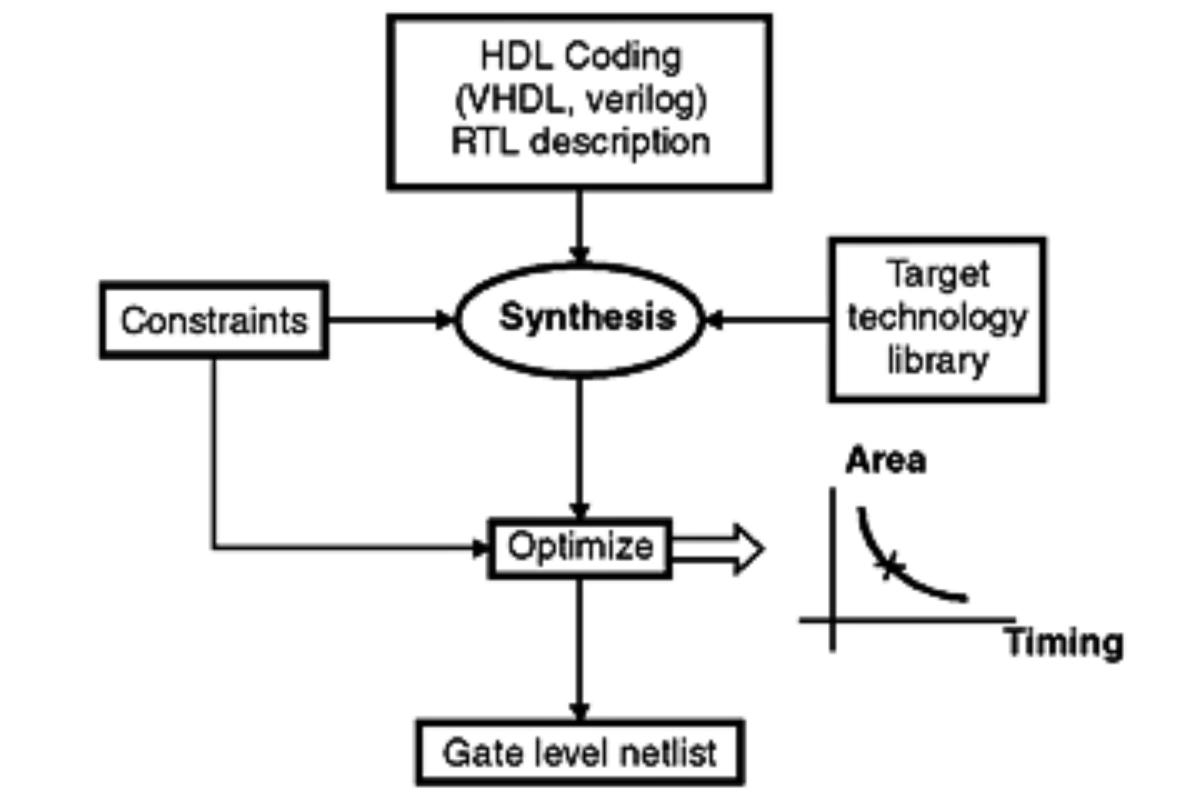

Công cụ Synthesis là quá trình chuyển đổi mô tả mạch ở mức cao (Register Transfer Level – RTL) được viết bằng ngôn ngữ Verilog hoặc VHDL thành dạng netlist mô tả các cổng logic và kết nối giữa chúng. Quy trình này tự động chuyển đổi mô tả mạch ở mức cao thành dạng netlist mô tả cấp cổng logic và kết nối giữa chúng, đồng thời tối ưu hóa các yếu tố quan trọng như thời gian đáp ứng (timing), diện tích chip và mức tiêu thụ năng lượng. Quá trình này được tiến hành bằng việc dùng công cụ như Design Compiler của Synopsys, Encounter RTL Compiler XL của Cadence.

Các loại hình Synthesis

Synthesis đóng vai trò quan trọng trong quy trình thiết kế chip, và có hai loại hình chính: Synthesis Logic và Physical Aware Synthesis.

-

Logical Synthesis

Synthesis Logic là phương pháp tổng hợp thông dụng, tập trung vào xử lý thiết kế HDL (Verilog hoặc VHDL) và tạo ra netlist ở cấp cổng logic. Trong quá trình này, bộ biên dịch tối ưu hóa thiết kế dựa trên các ràng buộc đã được xác định trước, như tiêu chuẩn về thời gian, diện tích, và năng lượng. Synthesis Logic thường được áp dụng trong giai đoạn đầu của quy trình thiết kế ASIC, tập trung vào chức năng và hiệu suất logic của mạch.

-

Physical Aware Synthesis

Quá trình Physical Aware Synthesis yêu cầu sơ đồ tầng bổ sung DEF làm đầu vào, mô tả sơ lược về bố cục vật lý của chip như vị trí của cổng I/O, macro, thông tin tắc nghẽn và vùng trống, cùng với file hệ số RC để tính toán độ trễ đường dẫn chính xác hơn. Ưu điểm của Physical Aware Synthesis bao gồm cải thiện tỷ lệ PPA (Công suất, Hiệu năng, Diện tích), đồng bộ timing tốt hơn với giai đoạn PNR (Placement and Routing – Vị trí và Đi Tuyến), và giảm thời gian thực hiện.

Lựa chọn loại hình Synthesis phù hợp

Việc lựa chọn loại hình Synthesis phụ thuộc vào giai đoạn thiết kế và mục tiêu tối ưu hóa. Synthesis Logic phù hợp cho giai đoạn đầu, tập trung vào chức năng logic. Physical Aware Synthesis phù hợp cho các giai đoạn sau, khi cần cân nhắc cả yếu tố vật lý của chip.

Chức năng của công cụ Synthesis

Synthesis thực hiện việc chuyển đổi mã HDL (Verilog, VHDL) thành netlist, mô tả chi tiết các kết nối giữa các thành phần trong mạch điện tử. Netlist đóng vai trò như bản đồ chi tiết cho quá trình chế tạo chip, giúp xác định cấu trúc logic của mạch.

Tự động tối ưu hóa thiết kế để đạt hiệu quả tối ưu bao gồm:

-

Loại bỏ các phần tử không cần thiết, sắp xếp các thành phần hợp lý và tối ưu hóa bố trí mạch để giảm thiểu diện tích chip, giúp tiết kiệm chi phí sản xuất và tăng khả năng tích hợp.

-

Tối ưu hóa đường dẫn logic, sử dụng các kỹ thuật pipelining và gate array để tăng tốc độ xử lý của mạch, đáp ứng nhu cầu ngày càng cao về hiệu năng.

-

Synthesis lựa chọn các thành phần có mức tiêu thụ điện năng thấp, tối ưu hóa thuật toán và áp dụng các kỹ thuật quản lý năng lượng để giảm thiểu mức tiêu thụ điện năng, giúp thiết bị hoạt động bền bỉ và thân thiện với môi trường.

Synthesis tạo ra thư viện cell, bao gồm các cổng logic, bộ nhớ và các thành phần khác được sử dụng để xây dựng mạch điện tử. Thư viện cell đóng vai trò như bộ sưu tập các khối xây dựng cơ bản, giúp cho quá trình thiết kế mạch trở nên nhanh chóng và hiệu quả hơn.

Cung cấp khả năng mô phỏng để kiểm tra và xác minh chức năng của thiết kế trước khi chế tạo. Quá trình mô phỏng giúp phát hiện và sửa lỗi sớm, tiết kiệm thời gian và chi phí cho việc sản xuất chip.

Điểm nổi bật của công cụ Synthesis so với các công cụ thiết kế khác

1. Tự động hóa thông minh

Synthesis tự động hóa hầu hết các bước thiết kế, từ chuyển đổi mã HDL đến tối ưu hóa mạch điện, giải phóng kỹ sư khỏi những công việc thủ công tẻ nhạt và tốn thời gian. Nhờ tự động hóa, thời gian thiết kế được rút ngắn đáng kể, giúp đẩy nhanh quá trình đưa sản phẩm ra thị trường, tạo lợi thế cạnh tranh cho doanh nghiệp. Giúp giảm thiểu nguy cơ sai sót do con người, đảm bảo độ chính xác và tính tin cậy cao cho thiết kế.

2. Hiệu suất tối ưu

Tối ưu hóa bố trí mạch điện, giúp thu nhỏ kích thước vi mạch, tiết kiệm chi phí sản xuất và nâng cao tính di động cho thiết bị. Tối ưu cấu trúc logic, giúp tăng tốc độ xử lý thông tin, mức tiêu thụ điện năng, giúp kéo dài thời lượng pin cho thiết bị di động và giảm thiểu tác động môi trường, đáp ứng nhu cầu ngày càng cao về hiệu năng của các thiết bị điện tử.

3. Khả năng mở rộng vô hạn

Công cụ Synthesis có khả năng xử lý các thiết kế vi mạch với độ phức tạp cao, bao gồm cả những mạch có hàng triệu cổng logic, đáp ứng nhu cầu thiết kế ngày càng tinh vi. Giúp kỹ sư giải quyết các dự án lớn một cách hiệu quả, nâng cao năng suất làm việc và đẩy nhanh tiến độ phát triển sản phẩm.

4. Dễ dàng sử dụng

Synthesis cung cấp giao diện trực quan, dễ sử dụng, giúp người dùng nhanh chóng nắm bắt và thao tác, ngay cả với những người mới bắt đầu. Hỗ trợ nhiều ngôn ngữ lập trình HDL phổ biến như Verilog và VHDL, giúp kỹ sư linh hoạt lựa chọn ngôn ngữ phù hợp với nhu cầu. Cộng đồng người dùng Synthesis rộng lớn luôn sẵn sàng chia sẻ kiến thức và kinh nghiệm, giúp bạn giải quyết mọi vấn đề encountered trong quá trình sử dụng.

Vai trò của công cụ Synthesis trong thiết kế vi mạch

Tăng tốc độ thiết kế: Bằng cách tự động hóa các bước quan trọng trong quy trình thiết kế, Synthesis giúp rút ngắn thời gian cần thiết cho việc phát triển mạch điện tử. Điều này giúp tăng tốc độ ra thị trường của sản phẩm, cho phép các doanh nghiệp cạnh tranh mạnh mẽ hơn trên thị trườn

Nâng cao chất lượng thiết kế: Synthesis không chỉ giúp tối ưu hóa thiết kế về mặt hiệu suất, mà còn giúp tạo ra các thiết kế vi mạch có độ tin cậy cao. Bằng cách tối ưu hóa cấu trúc logic và bố trí mạch, Synthesis đảm bảo rằng sản phẩm cuối cùng hoạt động ổn định và đáp ứng được các yêu cầu chức năng.

Giảm chi phí thiết kế: Synthesis giúp giảm thiểu chi phí phát triển vi mạch bằng cách tự động hóa các bước trong quy trình thiết kế. Việc giảm thiểu sự can thiệp của con người cũng giúp giảm bớt các sai sót và tăng hiệu suất làm việc. Điều này không chỉ giúp tiết kiệm chi phí mà còn làm giảm thời gian cần thiết cho việc phát triển sản phẩm.

Cách viết Verilog phù hợp với quy trình Synthesis

Để viết mã Verilog phù hợp với quy trình Synthesis, có một số nguyên tắc và hướng dẫn cụ thể như sau:

-

Sử dụng mã Verilog tổng hợp được: Tránh sử dụng các từ khóa hoặc cú pháp không được công cụ Synthesis hỗ trợ như “initial”, “fork join”, “force and release”, “real”. Thay vào đó, hãy sử dụng các cấu trúc và từ khóa mà công cụ Synthesis có thể hiểu và biên dịch thành logic cổng hoặc mạch logic phức tạp.

-

Tuân thủ “thiết kế để tổng hợp”: Đảm bảo rằng mã Verilog bạn viết được thiết kế để có thể tổng hợp một cách hiệu quả. Lựa chọn cấu trúc mạch và phong cách viết mã phù hợp để tối ưu hóa kết quả Synthesis, đảm bảo hiệu quả cao về mặt timing, diện tích và năng lượng. Hãy tập trung vào việc viết mã Verilog mô tả chức năng logic một cách rõ ràng và hiệu quả.

-

Kiểm tra và tối ưu hóa mã Verilog: Sử dụng các công cụ phân tích tĩnh để phát hiện lỗi cú pháp và tối ưu hóa mã Verilog trước khi tiến hành Synthesis. Điều này giúp đảm bảo rằng mã của bạn không có lỗi và sẵn sàng để được tổng hợp một cách chính xác và hiệu quả. Các công cụ này cũng có thể giúp bạn tối ưu hóa mã để đạt được hiệu suất và diện tích tốt nhất.

Với các nguyên tắc và hướng dẫn trên, bạn có thể viết mã Verilog phù hợp với quy trình Synthesis một cách hiệu quả và đảm bảo rằng sản phẩm cuối cùng đáp ứng được các yêu cầu về hiệu suất và chất lượng.

Khi tham gia khóa học Thiết kế vi mạch bán dẫn của FPT Jetking, tại Học kỳ III của khóa học bạn sẽ được tiếp xúc với quy trình Synthesis cùng những công cụ và phần mềm liên quan như Công cụ Cadence, Synopsis, Mentor graphics,… cùng với đó là về phát triển thiết kế RTL code với Verilog và VHDL. Bạn còn chần chờ gì mà không tham gia khóa học đào tạo thiết kế vi mạch bán dẫn tại FPT Jetking. Đến với FJK để trở thành những chuyên viên xuất sắc trong lĩnh vực Thiết kế vi mạch.